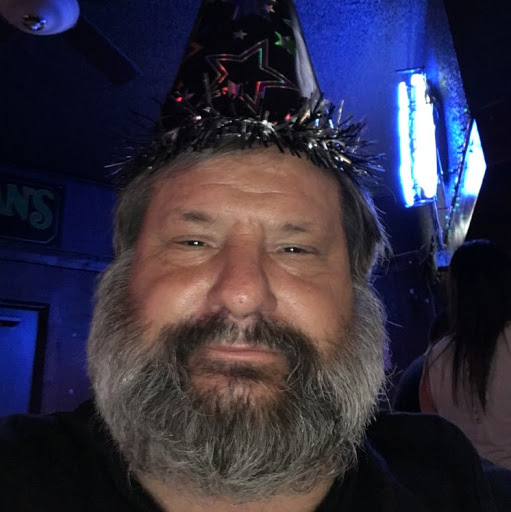

Alan J Drake

age ~53

from Round Rock, TX

- Also known as:

-

- Alan James Drake

- Alan A Drake

- Alana Drake

- Phone and address:

-

2317 Mockingbird Dr, Round Rock, TX 78681

5122183950

Alan Drake Phones & Addresses

- 2317 Mockingbird Dr, Round Rock, TX 78681 • 5122183950

- 2303 Stone Rd, Ann Arbor, MI 48105 • 7347641281

- 2338 Stone Rd, Ann Arbor, MI 48105 • 7347630059

- 2600 Gracy Farms Ln, Austin, TX 78758 • 5123391298

- Tucson, AZ

Us Patents

-

High Frequency Ring Oscillator With Feed-Forward Paths

view source -

US Patent:7321269, Jan 22, 2008

-

Filed:Jul 19, 2005

-

Appl. No.:11/184352

-

Inventors:Alan J. Drake - Round Rock TX, US

Fadi H. Gebara - Austin TX, US

Jeremy D. Schaub - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H03K 3/03

H03B 27/00 -

US Classification:331 57, 331 45, 331183

-

Abstract:An inverting circuit comprises a first inverter in a main path having a first input and a common ouput. A second inverter receives the first input and is coupled with a first voltage controlled pass gate to the common output. A third inverter couples a second input to the common output using a second voltage controlled pass gate. A fourth inverter couples the second input to the common output using the first voltage controlled pass gate. A ring oscillator is formed using a number N of the inverting circuits with each common output coupled to the first inputs forming a main ring of a ring oscillator. The second inputs are coupled to feed-forward signals from selected outputs. The resulting signals at the common outputs are an interpolation of the first and second input signals modulated by a control voltage coupled to the first and second pass gates.

-

Method And Apparatus For Soft-Error Immune And Self-Correcting Latches

view source -

US Patent:7415645, Aug 19, 2008

-

Filed:Jul 28, 2005

-

Appl. No.:11/191655

-

Inventors:Alan J. Drake - Round Rock TX, US

AJ Klein Osowski - Austin TX, US

Andrew K. Martin - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G01R 31/28

-

US Classification:714724

-

Abstract:A scanned value is stored by loading the value into at least three latch stages, generating an output value based on a majority of the latch stage outputs, and feeding the output value back to the inputs of the latch stages to reload the latch stages with the latch circuit output value. Refreshing of the latch stages in this manner repairs any upset latch stage and restores the latch circuit to its original scanned state. The latch circuit may be repeatedly refreshed, preferably on a periodic basis, to prevent failures arising from multiple upsets. The feedback path may include a front-end multiplexer which receives the scan-in line and the output of the majority gate. Control logic selects the output value from the majority gate to pass to the latch stages during the refresh phase. The latch stages may be arranged in a master-slave configuration with a check stage at the slave level. The method is particularly suited for self-correcting scan latches of a microprocessor control system.

-

Self-Resetting, Self-Correcting Latches

view source -

US Patent:7418641, Aug 26, 2008

-

Filed:Oct 3, 2005

-

Appl. No.:11/242491

-

Inventors:Alan J. Drake - Round Rock TX, US

Aj KleinOsowski - Austin TX, US

Andrew K. Martin - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G01R 31/28

G06F 11/08 -

US Classification:714726, 714797

-

Abstract:A latch circuit having three latch stages generates a majority output value from the stages, senses when the latch stage outputs are not all equal, and feeds the majority output value back to inputs of the latch stages to reload the latch stages. The latch circuit uses a not-equal gate whose output is an error signal that can be monitored to determine when a single-event upset has occurred. A master stage is controlled by a first multiplexer which receives one system clock signal, while a slave stage is controlled by a second multiplexer which receives another system clock signal, and the latch stage outputs are connected to respective inputs of the not-equal gate, whose output is connected to second inputs of the multiplexers. The latch circuit is part of a latch control system, and reloading of the latch stages takes less than one cycle of the system clock (less than 500 picoseconds).

-

Calibration Of Multi-Metric Sensitive Delay Measurement Circuits

view source -

US Patent:7542862, Jun 2, 2009

-

Filed:May 18, 2007

-

Appl. No.:11/750475

-

Inventors:Harmander Singh - Austin TX, US

Alan J. Drake - Round Rock TX, US

Fadi H. Gebara - Austin TX, US

John P. Keane - Minneapolis MN, US

Jeremy D. Schaub - Austin TX, US

Robert M. Senger - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G01R 29/02

G01R 29/00

G01R 35/00

G01D 18/00

G01P 21/00 -

US Classification:702 89, 702 79, 702 80

-

Abstract:A method and system for calibration of multi-metric sensitive delay measurement circuits provides for reduction of process-dependent variation in delays and their sensitivities to circuit metrics. A process corner for the delay circuit(s) is determined from at least one delay measurement for which the variation of delay due to process variation is previously characterized. The delay measurement(s) is made at a known temperature(s), power supply voltage(s) and known values of any other environmental metric which the delay circuit is designed to measure. Coefficients for delay versus circuit metrics are then determined from the established process corner, so that computation of circuit metric values from the delay measurements have improved accuracy and reduced variation due to the circuit-to-circuit and/or die-to-die process variation of the delay circuits.

-

Correction Of Delay-Based Metric Measurements Using Delay Circuits Having Differing Metric Sensitivities

view source -

US Patent:7548823, Jun 16, 2009

-

Filed:May 18, 2007

-

Appl. No.:11/750385

-

Inventors:Harmander Singh - Austin TX, US

Alan J. Drake - Round Rock TX, US

Fadi H. Gebara - Austin TX, US

John P. Keane - Minneapolis MN, US

Jeremy D. Schaub - Austin TX, US

Robert M. Senger - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G01R 29/00

-

US Classification:702 79, 700306, 702 57, 702136

-

Abstract:Correction of delay-based metric measurements using delay circuits having differing metric sensitivities provides improved accuracy for environmental and other circuit metric measurements that used delay lines. A delay line measurement, which may be a one-shot measurement or a ring oscillator frequency measurement is performed either simultaneously or sequentially using at least two delay lines that have differing sensitivities to a particular metric under measurement. A correction circuit or algorithm uses the measured delays or ring oscillator frequencies and corrects at least one of the metric measurements determined from one of the delays or ring oscillator frequencies in conformity with the other delay or ring oscillator frequency. The delays may be inverter chains, with one chain having a higher sensitivity to supply voltage than the other delay chain, with the other delay chain having a higher sensitivity to temperature. Temperature results can then be corrected for supply voltage variation and vice-versa.

-

Circuit For Dynamic Circuit Timing Synthesis And Monitoring Of Critical Paths And Environmental Conditions Of An Integrated Circuit

view source -

US Patent:7576569, Aug 18, 2009

-

Filed:Oct 13, 2006

-

Appl. No.:11/549138

-

Inventors:Gary D. Carpenter - Austin TX, US

Alan J. Drake - Round Rock TX, US

Harmander S. Deogun - Austin TX, US

Michael S. Floyd - Austin TX, US

Norman K. James - Liberty Hill TX, US

Robert M. Senger - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G01R 29/02

G06F 17/50

H03K 5/22 -

US Classification:327 14, 327 24, 716 14, 716 18

-

Abstract:A circuit for dynamically monitoring the operation of an integrated circuit under differing temperature, frequency, and voltage (including localized noise and droop), and for detecting early life wear-out mechanisms (e. g. , NBTI, hot electrons).

-

Method And Apparatus For Soft-Error Immune And Self-Correcting Latches

view source -

US Patent:7590907, Sep 15, 2009

-

Filed:Jul 6, 2008

-

Appl. No.:12/168147

-

Inventors:Alan J. Drake - Round Rock TX, US

AJ KleinOsowski - Austin TX, US

Andrew K. Martin - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G01R 31/28

-

US Classification:714726

-

Abstract:A scanned value is stored by loading the value into at least three latch stages, generating an output value based on a majority of the latch stage outputs, and feeding the output value back to the inputs of the latch stages to reload the latch stages with the latch circuit output value. Refreshing of the latch stages in this manner repairs any upset latch stage and restores the latch circuit to its original scanned state. The latch circuit may be repeatedly refreshed, preferably on a periodic basis, to prevent failures arising from multiple upsets. The feedback path may include a front-end multiplexer which receives the scan-in line and the output of the majority gate. Control logic selects the output value from the majority gate to pass to the latch stages during the refresh phase. The latch stages may be arranged in a master-slave configuration with a check stage at the slave level. The method is particularly suited for self-correcting scan latches of a microprocessor control system.

-

Digital Duty Cycle Corrector

view source -

US Patent:7667513, Feb 23, 2010

-

Filed:Nov 12, 2004

-

Appl. No.:10/988454

-

Inventors:Gary D. Carpenter - Austin TX, US

Alan J. Drake - Round Rock TX, US

Fadi H. Gebara - Austin TX, US

Chandler T. McDowell - Austin TX, US

Hung C. Ngo - Austin TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:H03K 3/017

-

US Classification:327175, 327172

-

Abstract:A circuit and method of correcting the duty cycle of digital signals is disclosed. The duty cycle of an input digital signal is measured and compared to a desired duty cycle. The leading edge of the input digital signal is passed to an output. The circuit and method adjust the falling edges at the output to achieve the desired duty cycle. The falling edges occur in response to rising edges of a delayed version of the input digital signal.

Resumes

Technical Manager

view sourceLocation:

929 Kentucky St, New Orleans, LA 70117

Industry:

Semiconductors

Work:

Tsmc

Technical Manager

Ibm Mar 2004 - Mar 2014

Rsm

University of Michigan Jan 2002 - Mar 2004

Research Assistant

Ibm Jan 2001 - Dec 2001

Research Internship

Technical Manager

Ibm Mar 2004 - Mar 2014

Rsm

University of Michigan Jan 2002 - Mar 2004

Research Assistant

Ibm Jan 2001 - Dec 2001

Research Internship

Education:

University of Michigan 2001 - 2005

Doctorates, Doctor of Philosophy, Electronics Engineering, Philosophy, Electronics University of Michigan 1998 - 2001

Master of Science, Masters, Electronics Engineering University of Arizona 1990 - 1997

Bachelors, Bachelor of Science, Electrical Engineering

Doctorates, Doctor of Philosophy, Electronics Engineering, Philosophy, Electronics University of Michigan 1998 - 2001

Master of Science, Masters, Electronics Engineering University of Arizona 1990 - 1997

Bachelors, Bachelor of Science, Electrical Engineering

Skills:

Ic

Semiconductors

Eda

Asic

Microprocessors

Computer Architecture

Cmos

Vlsi

Perl

Cloud Computing

Mixed Signal

Leadership

Vhdl

Testing

Circuit Design

Management

Simulations

Enterprise Software

Cadence

Spice

Manufacturing Test

Physical Design

Analog Circuit Design

Account Management

Software Testing

Circuit Board Design

Low Voltage Design

Semiconductors

Eda

Asic

Microprocessors

Computer Architecture

Cmos

Vlsi

Perl

Cloud Computing

Mixed Signal

Leadership

Vhdl

Testing

Circuit Design

Management

Simulations

Enterprise Software

Cadence

Spice

Manufacturing Test

Physical Design

Analog Circuit Design

Account Management

Software Testing

Circuit Board Design

Low Voltage Design

Interests:

Home Repair

Diy

Scouting

Piano

Singing

Auto Repair

Pipe and Electric Organ

Diy

Scouting

Piano

Singing

Auto Repair

Pipe and Electric Organ

Languages:

Spanish

Alan Drake

view source

Alan Drake

view source

Self Employed

view sourceWork:

Paradise Sheds

Self Employed

Self Employed

Alan Drake

view source

Alan Drake

view source

Alan Drake

view source

Alan Drake

view sourceMedicine Doctors

Alan R. Drake

view sourceSpecialties:

Family Medicine

Work:

Alan R Drake MD

133 Churchill Dr, Sparta, TN 38583

9318363262 (phone), 9318363269 (fax)

133 Churchill Dr, Sparta, TN 38583

9318363262 (phone), 9318363269 (fax)

Education:

Medical School

Wayne State University School of Medicine

Graduated: 1982

Wayne State University School of Medicine

Graduated: 1982

Languages:

English

Description:

Dr. Drake graduated from the Wayne State University School of Medicine in 1982. He works in Sparta, TN and specializes in Family Medicine. Dr. Drake is affiliated with St. Thomas Highlands Hospital.

Alan Ross Drake

view sourceSpecialties:

Family Medicine

Gynecology

Gynecology

Education:

Wayne State University (1982)

License Records

Alan A Drake

License #:

7345 - Expired

Category:

Water Operator

Issued Date:

Oct 28, 1999

Effective Date:

Jul 26, 2004

Expiration Date:

Dec 31, 2002

Type:

Provisional Grade IV Water Operator

Alan C Drake

License #:

256 - Active

Category:

Body Art

Issued Date:

Apr 1, 2009

Effective Date:

Jul 1, 2011

Expiration Date:

Mar 31, 2019

Type:

Tattoo Artist

Classmates

Alan Drake

view sourceSchools:

Tuscaloosa Middle School Tuscaloosa AL 1964-1968, Tuscaloosa High School Tuscaloosa AL 1967-1971

Community:

Deloris Madison, William Price

Alan Drake

view sourceSchools:

Middlesex County Vo-Tech School Piscataway NJ 1979-1983

Community:

Gene Ksenzakovic, Jody Lamoreaux, Ron Hornby, Patrick Ferguson, Frank Crincoli, Carmela Santaguida

Alan Drake

view sourceSchools:

Arbor Elementary School Piscataway NJ 1969-1974, Schor Middle School Piscataway NJ 1975-1978

Community:

Jody Lamoreaux, Dawn Krzewski, Tina Stutz

Alan Drake, Kadoka High S...

view source

Schor Middle School, Pisc...

view sourceGraduates:

Alan Drake (1975-1978),

Merylin Sarmiento (1991-1993),

Lisa Gallo (1979-1982),

Steven Belyo (1987-1990)

Merylin Sarmiento (1991-1993),

Lisa Gallo (1979-1982),

Steven Belyo (1987-1990)

Arbor Elementary School, ...

view sourceGraduates:

Alan Drake (1969-1974),

Andre Batts (1998-1999),

Sara Maehr (1996-1998),

Dennis James (1976-1977),

Laura Alfieri (1934-1937),

Clinton Newton (1948-1954)

Andre Batts (1998-1999),

Sara Maehr (1996-1998),

Dennis James (1976-1977),

Laura Alfieri (1934-1937),

Clinton Newton (1948-1954)

Brown County High School,...

view sourceGraduates:

Alan Drake (1981-1985),

susan cox (1957-1961),

richard veith (1986-1990),

Carol Kleinlein (1958-1962)

susan cox (1957-1961),

richard veith (1986-1990),

Carol Kleinlein (1958-1962)

Greenville High School, G...

view sourceGraduates:

Clifford Phillips (1973-1977),

Shelia Knight (1966-1970),

Bobby Lee (1968-1972),

Leon McDonald (1944-1948),

Allen Drake (1976-1980)

Shelia Knight (1966-1970),

Bobby Lee (1968-1972),

Leon McDonald (1944-1948),

Allen Drake (1976-1980)

Youtube

Flickr

Drake Alan

view source

Alan Drake

view source

Alan Drake

view source

Alan Drake

view source

Alan Drake

view source

Alan Drake

view source

Jay Alan Drake

view source

Alan P Drake

view sourceMyspace

Googleplus

Alan Drake

Lived:

Round Rock, TX

Bisbee, AZ, USA

Tucson, AZ, USA

Ann Arbor, MI, USA

Austin, TX, USA

Round Rock, TX, USA

San Nicholas, Buenos Aires, Argentina

Buenos Aires, Buenos Aires, Argentina

Arrecifes, Buenos Aires, Argentina

Bisbee, AZ, USA

Tucson, AZ, USA

Ann Arbor, MI, USA

Austin, TX, USA

Round Rock, TX, USA

San Nicholas, Buenos Aires, Argentina

Buenos Aires, Buenos Aires, Argentina

Arrecifes, Buenos Aires, Argentina

Work:

IBM - RSM (2004)

University of Michigan - Grad Student (1997-2005)

AlliedSignal - Engineer (1994-1997)

US Army Electronic Proving Ground - Summer Intern (1990-1991)

University of Michigan - Grad Student (1997-2005)

AlliedSignal - Engineer (1994-1997)

US Army Electronic Proving Ground - Summer Intern (1990-1991)

Education:

University of Michigan - Electrical Engineering, University of Arizona - Electrical Engineering, Bisbee High School

Relationship:

Married

About:

I'm a hick from small town Arizona who loves sports and music, wastes too much time reading political debates, and loves to tinker.

Bragging Rights:

I re-modeled our bathroom myself.

Alan Drake

Work:

V.L. Concessions - Customer service / Maintenance (2003)

Education:

Montclair High School

Alan Drake

Education:

Ferris State University - Digital Animation and Game Design

Alan Drake

Alan Drake

Tagline:

Keepin' it real since '92

Alan Drake

Alan Drake

Alan Drake

Get Report for Alan J Drake from Round Rock, TX, age ~53