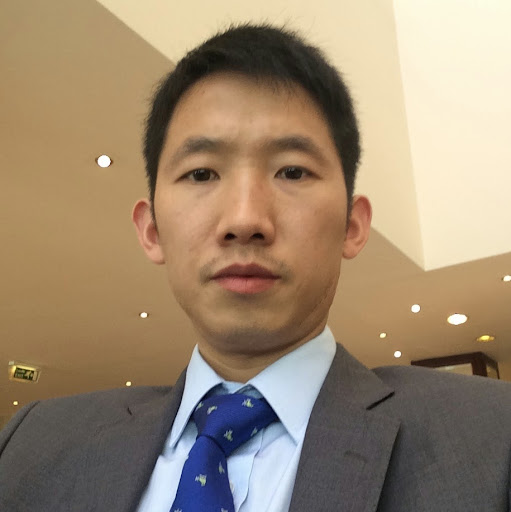

Bin Li Li

age ~50

from Phoenix, AZ

- Also known as:

-

- Bin L Li

- Li Bin Li

- Li Bin Bin Li

- Li B Li

- Li Libin

- Lin B Li

- Li Bin

- Bin Lili

- Phone and address:

-

8514 W Hazelwood St, Phoenix, AZ 85037

6232256084

Bin Li Phones & Addresses

- 8514 W Hazelwood St, Phoenix, AZ 85037 • 6232256084

- Rockville, MD

- Peoria, AZ

- Gaithersburg, MD

- Germantown, MD

- Cary, NC

- Hyattsville, MD

- El Mirage, AZ

Work

-

Company:A division of golden applexx coJun 2013

-

Position:Graphic designer

Education

-

School / High School:Claremont Graduate University2014

-

Specialities:M.F.A in Fine Art

Skills

Adobe Suite (InDesign • Illustrator • Photoshop) Maya Cinema 4D After Effec...

Isbn (Books And Publications)

Resumes

Bin Li

view sourceWork:

a division of GOLDEN APPLEXX CO

Jun 2013 to 2000

Graphic Designer REMODEL2 SYMPOSIUM

2010 to 2000

FREELANCE WSDEN HOME TEXTILE

Changsha, CN

Feb 2011 to Jan 2012

Commercial advertising design for marketing CHENGWEI ANIMATION

Changsha, CN

2010 to 2011

Graphic Designer / 3D Modeling Tutor

Jun 2013 to 2000

Graphic Designer REMODEL2 SYMPOSIUM

2010 to 2000

FREELANCE WSDEN HOME TEXTILE

Changsha, CN

Feb 2011 to Jan 2012

Commercial advertising design for marketing CHENGWEI ANIMATION

Changsha, CN

2010 to 2011

Graphic Designer / 3D Modeling Tutor

Education:

Claremont Graduate University

2014

M.F.A in Fine Art Qing Dao University

2009

B.A in Graphic design

2014

M.F.A in Fine Art Qing Dao University

2009

B.A in Graphic design

Skills:

Adobe Suite (InDesign, Illustrator, Photoshop) Maya Cinema 4D After Effects Microsoft Office Suite

Name / Title

Company / Classification

Phones & Addresses

Resident Associate

University of Washington

Computer Programming Services

Computer Programming Services

Phoenix, AZ 85004

Senior Software Architect

Futurewei Technologies, Inc.

Computer Programming Services

Computer Programming Services

1700 Alma Dr Ste 100, Phoenix, AZ 85004

Vice-President

Stone World Inc

Trade Contractor Mfg Wood Partitions/Fixtures

Trade Contractor Mfg Wood Partitions/Fixtures

25358 Pleasant Vly Rd, Fairfax, VA 20152

5712395167

5712395167

Director

China Media Inc

NAN ZHOU HAND DRAWN NOODLE HOUSE LLC

111 S Dobson Rd #108, Mesa, AZ 85202

2415 W Shawnee Dr, Chandler, AZ 85224

2415 W Shawnee Dr, Chandler, AZ 85224

Dean

Hope Chinese School Inc

School/Educational Services

School/Educational Services

10601 Mist Hvn Ter, Rockville, MD 20852

3019848888

3019848888

Manager, Owner

ASIANA COMMUNICATIONS LLC

Prepackaged Software Services

Prepackaged Software Services

995 E Baseline Rd #2034, Tempe, AZ 85283

3202 E Bellevue #26, Tucson, AZ 85716

3202 E Bellevue #26, Tucson, AZ 85716

Us Patents

-

Circuit For Filtering Single Event Effect (See) Induced Glitches

view source -

US Patent:6392474, May 21, 2002

-

Filed:Aug 30, 2000

-

Appl. No.:09/651156

-

Inventors:Bin Li - Fairfax VA

Dave C. Lawson - Hartwood VA

Joseph Yoder - Oakton VA -

Assignee:BAE Systems Information and Electronic Systems Integration Inc. - Rockville MD

-

International Classification:H03K 500

-

US Classification:327551, 327208, 327210

-

Abstract:A circuit for filtering single event effect (SEE) induced glitches is disclosed. The circuit for filtering SEE induced glitches comprises an SEE immune latch circuit and a delay element. The SEE immune latch circuit includes a first input, a second input, and an output. The SEE immune latch changes from one state to another state only upon having incoming input signals of identical polarity being applied contemporaneously at both the first input and the second input. The first input of the SEE immune latch circuit is directly connected to a signal input, and the second input of the SEE immune latch circuit is connected to the signal input via the delay element. The delay element provides a signal delay time equal to or greater than a pulse width of an SEE induced glitch but less than a pre-determined pulse width of an incoming signal at the signal input under normal operation. By connecting the delay element between the signal input and the second input of the SEE immune latch circuit, a temporal separation greater that the duration of an SEE induced glitch can be achieved on the data being drive into the first and the second inputs of the SEE immune latch circuit. As a result, SEE induced glitches will not be written into the SEE immune latch circuit.

-

Circuit For Accessing A Chalcogenide Memory Array

view source -

US Patent:6944041, Sep 13, 2005

-

Filed:Mar 26, 2004

-

Appl. No.:10/811454

-

Inventors:Bin Li - Chantilly VA, US

Kenneth R. Knowles - Manassas VA, US

David C. Lawson - Haymarket VA, US -

Assignee:BAE Systems Information and Electronic Systems Integration, Inc. - Nashua NH

-

International Classification:G11C013/00

G11C011/00 -

US Classification:365113, 365163

-

Abstract:A circuit for accessing a chalcogenide memory array is disclosed. The chalcogenide memory array includes multiple subarrays with rows and columns formed by chalcogenide storage elements. The chalcogenide memory array is accessed by discrete read and write circuits. Associated with a respective one of the subarrays, each of the write circuits includes an independent write 0 circuit and an independent write 1 circuit. Also associated with a respective one of the subarrays, each of the read circuits includes a sense amplifier circuit. In addition, a voltage level control module is coupled to the read and write circuits to ensure that voltages across the chalcogenide storage elements within the chalcogenide memory array do not exceed a predetermined value during read and write operations.

-

Read/Write Circuit For Accessing Chalcogenide Non-Volatile Memory Cells

view source -

US Patent:6965521, Nov 15, 2005

-

Filed:Jul 31, 2003

-

Appl. No.:10/631174

-

Inventors:Bin Li - Chantilly VA, US

Kenneth R. Knowles - Manassas VA, US

David C. Lawson - Haymarket VA, US -

Assignee:BAE Systems, Information and Electronics Systems Integration, Inc. - Nashua NH

-

International Classification:G11C011/00

-

US Classification:365148, 365163, 365113, 36518901

-

Abstract:A read/write circuit for accessing chalcogenide non-volatile memory cells is disclosed. The read/write circuit includes a chalcogenide storage element, a voltage limiting circuit, a current-to-voltage converter, and a buffer circuit. The voltage limiting circuit, which is coupled to the chalcogenide storage element, ensures that voltages across the chalcogenide storage element will not exceed a predetermined value during a read operation. During a read operation, the current-to-voltage converter, which is coupled to the voltage limiting circuit, converts a current pulse read from the chalcogenide storage element to a voltage pulse. By sensing the voltage pulse from the current-to-voltage converter, the buffer circuit can determine a storage state of the chalcogenide storage element.

-

Read/Write Circuit For Accessing Chalcogenide Non-Volatile Memory Cells

view source -

US Patent:7099187, Aug 29, 2006

-

Filed:Sep 14, 2005

-

Appl. No.:11/225953

-

Inventors:Bin Li - Chantilly VA, US

Kenneth R. Knowles - Manassas VA, US

David C. Lawson - Haymarket VA, US -

Assignee:BAE Systems Information and Electronic Systems Integration Inc. - Nashua NH

Ovonyx, Inc. - Rochester Hills MI -

International Classification:G11C 11/00

-

US Classification:365163, 365113

-

Abstract:A read/write circuit for accessing chalcogenide non-volatile memory cells is disclosed. The read/write circuit includes a chalcogenide storage element, a voltage limiting circuit, a current-to-voltage converter, and a buffer circuit. The voltage limiting circuit, which is coupled to the chalcogenide storage element, ensures that voltages across the chalcogenide storage element will not exceed a predetermined value during a read operation. During a read operation, the current-to-voltage converter, which is coupled to the voltage limiting circuit, converts a current pulse read from the chalcogenide storage element to a voltage pulse. By sensing the voltage pulse from the current-to-voltage converter, the buffer circuit can determine a storage state of the chalcogenide storage element.

-

Read Reference Circuit For A Sense Amplifier Within A Chalcogenide Memory Device

view source -

US Patent:7916527, Mar 29, 2011

-

Filed:Nov 26, 2008

-

Appl. No.:12/525482

-

Inventors:Bin Li - Chantilly VA, US

Adam Matthew Bumgarner - Duluth GA, US

Daniel Pirkl - Centreville VA, US -

Assignee:BAE Systems Information and Electronic Systems Integration Inc. - Nashua NH

Ovonyx, Inc. - Rochester Hills MI -

International Classification:G11C 11/00

-

US Classification:365163, 365203, 36518909

-

Abstract:A read reference circuit for a sense amplifier within a chalcogenide memory device is disclosed. The read reference circuit provides a reference voltage level to the sense amplifier for distinguishing between a logical “0” state and a logical “1” state within a chalcogenide memory cell. In conjunction with a precharge circuit, the read reference circuit generates a selectable read reference current to the sense amplifier in order to detect the logical state of the chalcogenide memory cell. The precharge circuit precharges the bitlines of the chalcogenide memory cell before the sense amplifier detects the logical state of the chalcogenide memory cell.

-

Hardened Current Mode Logic (Cml) Voter Circuit, System And Method

view source -

US Patent:7965098, Jun 21, 2011

-

Filed:Dec 10, 2008

-

Appl. No.:12/595865

-

Inventors:Neil Wood - Centreville CA, US

David Rea - Manassas VA, US

Bin Li - Chantilly VA, US -

Assignee:BAE Systems Information and Electronic Systems Integration Inc. - Nashua NH

-

International Classification:H03K 19/003

H03K 19/096

H03L 7/00 -

US Classification:326 11, 326 95, 327144

-

Abstract:A current mode logic voter circuit includes three two-input split NOR gates. Each two-input split NOR gate receives a corresponding pair of input signals and generates a pair of first output signals responsive to the input signals. A three input split NOR gate is coupled to the two-input split NOR gates to receive the first output signals and generates a second pair of output signals responsive to the first output signals from the two-input split NOR gates. The two and three-input split NOR gates can be formed from current mode logic buffer circuits, and in one embodiment in the three-input split NOR gate the buffer circuits are hardened.

-

Non-Volatile Single-Event Upset Tolerant Latch Circuit

view source -

US Patent:7965541, Jun 21, 2011

-

Filed:Nov 25, 2008

-

Appl. No.:12/525458

-

Inventors:Bin Li - Chantilly VA, US

John C. Rodgers - Fairfax VA, US

Nadim F. Haddad - Oakton VA, US -

Assignee:BAE Systems Information and Electronic Systems Integration Inc. - Nashua NH

Ovonyx, Inc. - Rochester Hills MI -

International Classification:G11C 11/00

-

US Classification:365156, 365154, 365163

-

Abstract:A non-volatile single-event upset (SEU) tolerant latch is disclosed. The non-volatile SEU tolerant latch includes a first and second inverters connected to each other in a cross-coupled manner. The gates of transistors within the first inverter are connected to the drains of transistors within the second inverter via a first feedback resistor. Similarly, the gates of transistors within the second inverter are connected to the drains of transistors within the first inverter via a second feedback resistor. The non-volatile SEU tolerant latch also includes a pair of chalcogenide memory elements connected to the inverters for storing information.

-

Analog Access Circuit For Validating Chalcogenide Memory Cells

view source -

US Patent:7986550, Jul 26, 2011

-

Filed:Nov 26, 2008

-

Appl. No.:12/525510

-

Inventors:Bin Li - Chantilly VA, US

Adam Matthew Bumgarner - Duluth GA, US -

Assignee:BAE Systems Information and Electronics Systems Integration Inc. - Nashua NH

Ovonyx, Inc. - Rochester Hills MI -

International Classification:G11C 7/00

-

US Classification:365163, 36518915, 365151

-

Abstract:An analog access circuit for characterizing chalcogenide memory cells is disclosed. The analog access circuit includes an analog access control module, an address and data control module, and an analog cell access and current monitoring module. The analog access control module selectively controls whether a normal memory access or an analog memory access should be performed on a specific chalcogenide memory cell. The address and data control module allows a normal memory access to the chalcogenide memory cell according to an input address. The analog cell access and current monitoring module performs an analog memory access to the chalcogenide memory cell according to the input address, and monitors a reference current from a sense amplifier associated with the chalcogenide memory cell.

Lawyers & Attorneys

Bin Li - Lawyer

view sourceOffice:

Law Offices of Bin Li & Associates

Specialties:

Business

ISLN:

921007447

Admitted:

2002

University:

Southwestern Univ SOL; Southwestern Univ SOL; Los Angeles CA; Los Angeles CA; Foreign School; Foreign School

Bin Li

view source

Hyun Bin Li

view source

Bin Rui Li

view source

Bin Li Lee

view source

Bin Li

view source

Bin Li

view source

Bin Li

view source

Bin Li

view sourceMyspace

Googleplus

Bin Li

Education:

Brigham Young University - Accounting

About:

Via what ways to accomplish above dream? multi-disciplinary, integral.

Tagline:

I want to accomplish a lot of things in my life, not for me to leave a legacy, but for people, community, society, and the world.

Bragging Rights:

Multi-tasker; Creator; Designer

Bin Li

Bin Li

Tagline:

Smart is the new sexy

Bin Li

Education:

R.I.T. - FILM

About:

I am simply a filmmaker. =)

Bin Li

Education:

Nanjing University

Bin Li

Bin Li

Work:

Polycom - Sales Engineer

Bin Li

Work:

Wayne State University

Flickr

Youtube

Classmates

Bin LI, suny new paltz ny...

view source

Guilford Elementary Schoo...

view sourceGraduates:

Yahaya Yahaya Babangida (2004-2008),

Karl Trautner (2003-2007),

Bin LI (1998-2002),

Alexandris Clark (2003-2007),

Cindy Sampsell (1967-1971)

Karl Trautner (2003-2007),

Bin LI (1998-2002),

Alexandris Clark (2003-2007),

Cindy Sampsell (1967-1971)

University of Missouri, S...

view sourceGraduates:

Raymond Iggulden (1960-1964),

Bin LI (1989-1993),

Ryan Vines (2005-2009),

Joseph Nugent (1967-1971)

Bin LI (1989-1993),

Ryan Vines (2005-2009),

Joseph Nugent (1967-1971)

suny new paltz ny, New pa...

view sourceGraduates:

Bin LI (1997-2001),

Kenneth Munoz (1968-1972),

Robert McLean (1989-1993),

Marcia Wasserman (1950-1954),

Glen Burn (1975-1979),

Megan Fisher (2007-2008)

Kenneth Munoz (1968-1972),

Robert McLean (1989-1993),

Marcia Wasserman (1950-1954),

Glen Burn (1975-1979),

Megan Fisher (2007-2008)

Lansdale Catholic High Sc...

view sourceGraduates:

Danielle Clemens (1994-1998),

Kathleen Storrs (1973-1977),

Bin LI (1996-2000),

Jeannie Grosso (1980-1984)

Kathleen Storrs (1973-1977),

Bin LI (1996-2000),

Jeannie Grosso (1980-1984)

Get Report for Bin Li Li from Phoenix, AZ, age ~50