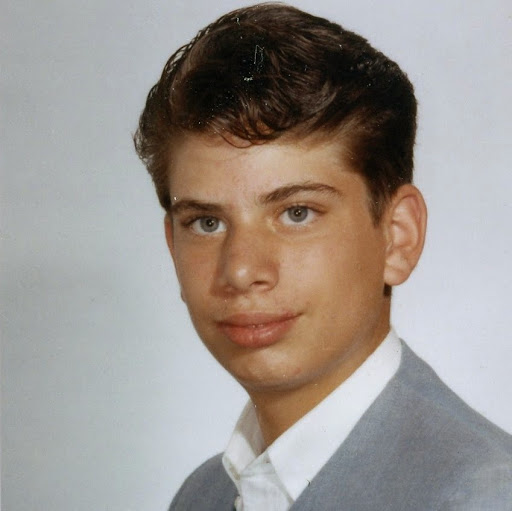

Bruce W Cheney

age ~74

from Sherwood, OR

- Also known as:

-

- Bruce Wilson Cheney

- Phone and address:

-

31925 Canter Ln, Sherwood, OR 97140

5036255747

Bruce Cheney Phones & Addresses

- 31925 Canter Ln, Sherwood, OR 97140 • 5036255747

- Somerville, MA

- Corvallis, OR

- Dallas, TX

Work

-

Position:Protective Service Occupations

Education

-

Degree:Graduate or professional degree

Emails

Isbn (Books And Publications)

Stress in Childhood: An Intervention Model for Teachers and Other Professionals

view sourceAuthor

Bruce D. Cheney

ISBN #

0807727806

Us Patents

-

Delay Equalization Emulation For High Speed Phase Modulated Direct Digital Synthesis

view source -

US Patent:51405407, Aug 18, 1992

-

Filed:Jul 30, 1990

-

Appl. No.:7/559795

-

Inventors:Bruce W. Cheney - Sherwood OR

Donald C. Larson - Beaverton OR

Arnold M. Frisch - Portland OR -

Assignee:TriQuint Semiconductor, Inc. - Beaverton OR

-

International Classification:G06F 102

-

US Classification:364718

-

Abstract:In a pipelined direct digital synthesis system (FIG. 3), new increment data (124) and/or phase modulation data (122) are input delay equalized by providing the data to a series of switch blocks (132), each switch block corresponding to a stage of the accumulator (124). Each switch block includes a multiplexer (132) for selecting among the new increment data, phase modulation data, and previously stored increment data, and includes a flip-flop circuit (134) for storing the selected increment data. A shift register (140) provides select signals (146) to each of the multiplexers. In operation, as a single bit propagates through the shift register, the select signals sequentially control the multiplexers to sequentially interleave blocks of selected increment data into respective accumulator stages in ascending order of binary significance. The invention thereby substantially reduces the input delay equalization circuitry necessary for coherent operation.

Resumes

Program Manager

view sourceLocation:

Portland, OR

Industry:

Semiconductors

Work:

Triquint Semiconductor

Program Manager

Program Manager

Education:

Cornell University

Bruce Cheney

view source

Bruce Cheney

view source

Bruce Cheney

view sourceLocation:

United States

Googleplus

Bruce Cheney

Bruce Cheney

Youtube

Myspace

Plaxo

Bruce Cheney

view sourceClifton Park, NYDirector of Technology at New Horizons Computer Le... Past: Senior System Engineer at sage computer associates, Senior Technical Instructor at New...

Rev. Bruce D. Cheney

view sourceOlive Branch, MSPriest at Holy Cross Episcopal Church Past: Student at Virginia Theological Seminary, LCDR (ret) at USCG

Rev. Bruce Cheney

view sourceOlive Branch, MS

Bruce Cheney

view sourceManager at ACBC Ltd

Flickr

Classmates

Bruce F (Cheney)

view sourceSchools:

Academy of St. Joseph South Berwick ME 1966-1970, South Berwick Junior High School South Berwick ME 1966-1970

Community:

Judith Grace

Bruce Cheney

view sourceSchools:

St. Lawrence Central High School Brasher Falls NY 1962-1966

Community:

Cleora Louey, Karen Barnes, Ann Richards, Carol Flint, Carolyn Montgomery, Susan Fregoe, Eleanor Blais, Henry Barse, Peggy Margaret, Richard Cudlipp

Bruce Cheney, Tilton Scho...

view source

Bruce Cheney | Greene Com...

view source

Bruce Cheney, Central Hig...

view source

Greene Community High Sch...

view sourceGraduates:

Bruce Cheney (1958-1962),

Scott Foster (1979-1983),

Karitta Vanorden (1998-2002),

Stephen Knight (1971-1975)

Scott Foster (1979-1983),

Karitta Vanorden (1998-2002),

Stephen Knight (1971-1975)

Lenny Bruce Cheney

view source

Richard Bruce Cheney

view source

Bruce Cheney Jr.

view source

Bruce Cheney

view source

Bruce Cheney

view source

Bruce Cheney

view source

Bruce Cheney

view source

Bruce Cheney

view sourceGet Report for Bruce W Cheney from Sherwood, OR, age ~74