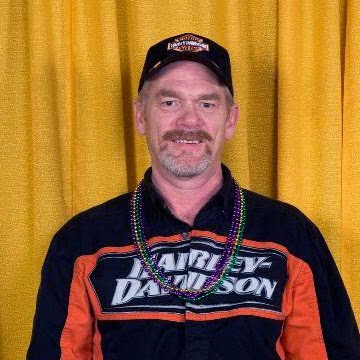

David C Burden

age ~47

from Cary, NC

- Also known as:

-

- David Christopher Burden

- David Christophe Burden

David Burden Phones & Addresses

- Cary, NC

- Fort Collins, CO

- Ann Arbor, MI

- San Mateo, CA

Wikipedia References

David Burden

Name / Title

Company / Classification

Phones & Addresses

Owner

D B Painting & Drywall Repair

Painters. Pressure Washing Companies. Drywall Contractors

Painters. Pressure Washing Companies. Drywall Contractors

PO Box 52735, Durham, NC 27717

9198121150

9198121150

APEX PACKAGING SUPPLIES, LLC

DB Painting and Drywall Repair

Drywall · House Painters · Interior Painters

Drywall · House Painters · Interior Painters

PO Box 52735, Durham, NC 27717

9198121150

9198121150

D B Painting

Drywall · Interior Painters · Wallpaper Removal · Wallpaper

Drywall · Interior Painters · Wallpaper Removal · Wallpaper

Po, Durham, NC 27717

PO Box 52735, Durham, NC 27717

9198121150

PO Box 52735, Durham, NC 27717

9198121150

President

Shimber Beris

Project Manager

County of Summit

Real Estate Agent/Manager General Government · Executive Office · Public Order/Safety · Legislative Body · Housing Program · Administrative Social/Manpower Programs · Treasurers Office · Community & Economic Development

Real Estate Agent/Manager General Government · Executive Office · Public Order/Safety · Legislative Body · Housing Program · Administrative Social/Manpower Programs · Treasurers Office · Community & Economic Development

3306432600, 3306432558, 3307612814, 3306432500

Resumes

3Par L4 Recovery Manager

view sourceLocation:

Fort Collins, CO

Industry:

Information Technology And Services

Work:

Hewlett-Packard

3Par L4 Recovery Manager

Hewlett-Packard Sep 2010 - Oct 2017

Storage Platforms Expert

Hp Sep 2010 - Oct 2015

Storage Platforms Expert

Hp 2007 - 2010

Nas Verification Specialist

Hp 1999 - 2007

Eda Software Designer

3Par L4 Recovery Manager

Hewlett-Packard Sep 2010 - Oct 2017

Storage Platforms Expert

Hp Sep 2010 - Oct 2015

Storage Platforms Expert

Hp 2007 - 2010

Nas Verification Specialist

Hp 1999 - 2007

Eda Software Designer

Education:

Stanford University 1999 - 2005

Master of Science, Masters, Computer Science University of Michigan 1995 - 1999

Bachelor of Science In Engineering, Bachelors, Computer Engineering

Master of Science, Masters, Computer Science University of Michigan 1995 - 1999

Bachelor of Science In Engineering, Bachelors, Computer Engineering

Contractor

view sourceWork:

Burden Builders

Contractor

Contractor

David Burden

view source

David Burden

view sourceWork:

Department of Veterans Affairs

Retired Arnp

Retired Arnp

Isbn (Books And Publications)

Biotechnology: Proteins to PCR : A Course in Strategies and Lab Techniques

view sourceAuthor

David W. Burden

ISBN #

0817637567

Biotechnology: Proteins to Pcr A Course in Strategies and Lab Techniques

view sourceAuthor

David W. Burden

ISBN #

0817638431

License Records

David Burden

License #:

7364 - Expired

Category:

Water Operator

Issued Date:

May 9, 1998

Effective Date:

Feb 11, 2008

Expiration Date:

Dec 31, 2007

Type:

Grade VI Water Operator

Us Patents

-

System For And Method Of Efficient Contact Pad Identification

view source -

US Patent:6484301, Nov 19, 2002

-

Filed:May 25, 2001

-

Appl. No.:09/865268

-

Inventors:David C Burden - Fort Collins CO

-

Assignee:Hewlett-Packard Company - Palo Alto CA

-

International Classification:G06F 1750

-

US Classification:716 8, 716 15, 716 19

-

Abstract:The present invention includes a system for and a method of identifying the location of contact pads on interconnect layers of printed circuit boards or metal layers of integrated circuits. The invention groups the conductive surfaces into rectangular areas and applies a mask to the identified rectangular areas by aligning a corner of the mask with the corresponding corner of the rectangular area. Once aligned, the remaining corners of the mask are checked to see whether there is an underlying conductive material present at all corners thereby identifying a suitable location for a contact pad. The invention further includes an alignment of alternate corners of the mask with the corresponding corner of the rectangular area if previous attempts to identify a contact pad were unsuccessful.

-

Exponential Increments In Fet Size Selection

view source -

US Patent:6691285, Feb 10, 2004

-

Filed:Aug 27, 2002

-

Appl. No.:10/229535

-

Inventors:David C. Burden - Fort Collins CO

Dave Anderson - Fort Collins CO -

Assignee:Hewlett-Packard Development Company, L.P. - Houston TX

-

International Classification:G06F 1750

-

US Classification:716 2, 716 4, 716 5, 716 6, 716 7, 716 8, 716 9, 716 10

-

Abstract:A set of discrete transistor sizes spread in an exponential manner over a specified range is the basis for adjusted transistor sizes used to optimize a circuit. One of the discrete transistor sizes may be the original transistor size or other starting point for the optimization.

-

Systems And Methods Of Cross-Over Current Calculation Within Electronic Designs

view source -

US Patent:6862715, Mar 1, 2005

-

Filed:Jul 29, 2002

-

Appl. No.:10/207578

-

Inventors:David C. Burden - Fort Collins CO, US

Matthew Biggi - Fort Collins CO, US

Jaime Weisberg - Fort Collins CO, US -

Assignee:Hewlett-Packard Development Company, L.P. - Houston TX

-

International Classification:G06F017/50

-

US Classification:716 2

-

Abstract:A process is shown for determining crossover current in a circuit design. One or more static CMOS gates are identified within the circuit design. One or more widths of at least one of a P-stack and N-stack associated with the CMOS gates are then determined. A voltage slope at the input of, and a capacitive load at the output of, one or more of the nodes are also determined. Crossover current, per static CMOS gate, is estimated based on the widths, the voltage slope and capacitive load. An overall crossover current is determined by summing individual gate-level crossover currents. The circuit design may be optimized for power consumption, for example, by modifying design elements of the circuit design while monitoring overall crossover current.

-

Systems And Methods For Generating An Artwork Representation According To A Circuit Fabrication Process

view source -

US Patent:6892374, May 10, 2005

-

Filed:Jun 19, 2002

-

Appl. No.:10/174674

-

Inventors:Bruno P. Melli - Windsor CO, US

David C. Burden - Fort Collins CO, US

Matthew L. Biggio - Fort Collins CO, US -

International Classification:G06F017/50

-

US Classification:716 19, 716 9, 716 10

-

Abstract:In one embodiment, the present invention relates to a system for generating an artwork representation according to a circuit fabrication process. The system comprises a cell library that stores at least dimensional information associated with a plurality of circuit cells, wherein each of the plurality of circuit cells is defined by a sub-mask for a respective logical device according to the circuit fabrication process; an instance placement engine that generates a circuit layout that is defined by at least a specification file specifying an arrangement of logical devices and the cell library; and an artwork generator that generates an artwork representation that defines a mask for etching of the generated circuit layout according to the circuit fabrication process.

-

Logic Gate Identification Based On Hardware Description Language Circuit Specification

view source -

US Patent:6904573, Jun 7, 2005

-

Filed:May 27, 2003

-

Appl. No.:10/446097

-

Inventors:David Burden - Fort Collins CO, US

-

Assignee:Hewlett-Packard Development Company, L.P. - Houston TX

-

International Classification:G06F017/50

-

US Classification:716 2, 716 6

-

Abstract:Techniques are disclosed for estimating the signal propagation delays within a circuit, based on a description of the circuit written in a hardware description language (HDL), such as a register transfer language (RTL). Assignment statements in the description which describe the performance of a logical function are modeled using logic gates which perform the function described. A particular function may be modeled using one or more logic gates depending on the number of inputs to the function. The delay associated with performance of the function is estimated by estimating the delay through the circuit used to model the function. Estimates for multiple functions may be combined to estimate the total delay associated with a particular signal path through a circuit.

-

Power Estimation Based On Power Characterizations

view source -

US Patent:7000204, Feb 14, 2006

-

Filed:Sep 2, 2003

-

Appl. No.:10/653650

-

Inventors:Tyson R. McGuffin - Fort Collins CO, US

Thomas W. Chen - Fort Collins CO, US

David C. Burden - Fort Collins CO, US -

Assignee:Hewlett-Packard Development Company, L.P. - Houston TX

-

International Classification:G06F 17/50

-

US Classification:716 5, 716 18

-

Abstract:Systems and methods are provided that can be utilized to estimate power associated with a circuit design. The estimated power is determined by employing power characterizations associated with dynamic and static power related parameters of a circuit design. The power characterizations can be determined prior to circuit design optimizations, stored and utilized during circuit design optimizations.

-

System And Method Of Processing A Circuit Design Via Critical Design Paths

view source -

US Patent:20040019473, Jan 29, 2004

-

Filed:Jul 24, 2002

-

Appl. No.:10/205332

-

Inventors:David Burden - Fort Collins CO, US

Tyson McGuffin - Fort Collins CO, US -

International Classification:G06F017/50

-

US Classification:703/014000

-

Abstract:A process for processing a circuit design. One or more critical design paths of the circuit design are determined. These paths may for example be determined relative to timing and/or current utilization. Design elements of the paths may be grouped by type (e.g., FETs, wires). The circuit design may be optimized by processing a reduced set of design elements as determined by the critical paths and grouping. Optimization may include modifying FET design element width, or a routing path of a wire design element, along a critical path of the design, and comparing the new optimization relative to preselected design goals such as timing and power consumption.

-

Method And System For Chromosome Correction In Genetic Optimazation Process

view source -

US Patent:20050021238, Jan 27, 2005

-

Filed:Jul 21, 2003

-

Appl. No.:10/624266

-

Inventors:Tyson McGuffin - Fort Collins CO, US

Thomas Chen - Fort Collins CO, US

Dave Anderson - Fort Collins CO, US

David Burden - Fort Collins CO, US -

International Classification:G06F019/00

G01N033/48

G01N033/50 -

US Classification:702020000

-

Abstract:The convergence speed of a computer-implemented genetic optimization process is improved through the correction of child chromosomes containing undesirable gene combinations. Undesirable gene combinations may be identified through application of heuristic techniques, statistical techniques, or a combination of the two.

Plaxo

David Burden

view sourceFlickr

Myspace

Googleplus

David Burden

Work:

Thatma.de - Designer/ Developer (2011)

KOJO - Developer (2012)

That Fresh - User Exerperience designer, designer (2009-2012)

Advance Support - Designer/ Front-end developer (2010-2011)

KOJO - Developer (2012)

That Fresh - User Exerperience designer, designer (2009-2012)

Advance Support - Designer/ Front-end developer (2010-2011)

Education:

University of South Australia - Bachelor of Visual Arts

Relationship:

Married

About:

Pinhole photographer, designer, fron-end person. Spent 9+ years living in Japan, currently in Australia. Love making a custom QR code and cooking up some Japanese soul food.

Tagline:

Torn between Australia and Japan

Bragging Rights:

Exhibited the first mobile phone artwork in Australia @ACP in Sydney.

David Burden

Tagline:

You know me from twitter Im dave_mann157 :)

David Burden

David Burden

David Burden

David Burden

David Burden

David Burden

Classmates

David Dave (Burden)

view sourceSchools:

Western Hills High School Western Hills OH 1983-1987

Community:

Tracy Curry, Natasha Newton, Yolanda Blackburn

David Burden

view sourceSchools:

West Lynn Heights High School Lynn Lake Palestinian Territory, Occupie 1981-1985

Community:

Leitta Magson, Marlene Johnson

David Burden

view sourceSchools:

Loyola Academy Wilmette IL 1984-1988

Community:

Charles Bidwill, Kandice Underhill, Michael Link

David Burden

view sourceSchools:

Camp Zama American High School Camp Zama PA 1990-1994

Community:

Jeffrey Elliott, Talitha Johnson, Kay Freeman, Phyllis Stewart

David Burden (Same)

view sourceSchools:

Milton High School Milton WV 1969-1973

Community:

Deborah Elkins, Lee Yates, Susan Becka, Anna Jarvis

David Houston (Burden)

view sourceSchools:

Birchcliff Heights Elementary School Toronto Morocco 1964-1972

Community:

Jeannie Macgregor, Suzanne Wilson, Catherine Drum, Sophia Kolaroff, Rick Price

David Burden

view sourceSchools:

Clifton Springs High School Clifton Springs NY 1961-1965

Community:

Patricia Maloney, Gail Lannon, Barbara Pelko, Gayle Dubois

Youtube

David Burden

view source

David Burden

view source

David Burden

view source

David Burden

view source

David Burden

view source

David J Burden

view source

David Burden

view source

David Burden

view sourceGet Report for David C Burden from Cary, NC, age ~47