David E Hutton

age ~56

from Mansfield, MA

- Also known as:

-

- Duane E Hutton

- Davide Hutton

- Phone and address:

- 1 Atwood St, Mansfield, MA 02048

David Hutton Phones & Addresses

- 1 Atwood St, Mansfield, MA 02048 s

- 114 N Main St #A, Mansfield, MA 02048 • 7742844127

- Poughkeepsie, NY

- Quincy, MA

- Brooklyn, NY

- Charlestown, MA

Education

-

Degree:Doctor of Jurisprudence/Juris Doctor (J.D.)

-

School / High School:California Western School of L

Ranks

-

Licence:Texas - Eligible To Practice In Texas

-

Date:1992

Name / Title

Company / Classification

Phones & Addresses

Pbx Manager

Communications Design Associates Inc

Engineering Services

Engineering Services

437 Tpke St, Canton, MA 02021

3395026551

3395026551

D & D LIMITED

WOODCHUCK TREE SERVICE LLC

President

IRENE MARY, INC

PO Box 165, South Weymouth, MA 02190

236 Water St, Pembroke, MA

236 Water St, Pembroke, MA

Manager

KRYPTONITE CORPORATION

Mfg Bicycle and Motorcycle Locks · Hardware Mfg

Mfg Bicycle and Motorcycle Locks · Hardware Mfg

320 Tpke St, Canton, MA 02021

437 Tpke St, Canton, MA 02021

7818286655, 7818280122, 7818214777

437 Tpke St, Canton, MA 02021

7818286655, 7818280122, 7818214777

HUTTON'S TAVERN, INC

Drinking Place

Drinking Place

12 E Main St, Wappingers Falls, NY 12590

2652 E Main St, New Hamburg, NY 12590

2652 E Main St, New Hamburg, NY 12590

President

Pyx Mining (U.S.) Inc

Resumes

David Hutton

view source

David Hutton

view source

David Hutton

view source

David Hutton

view source

David Hutton

view source

David Hutton

view source

David Hutton

view source

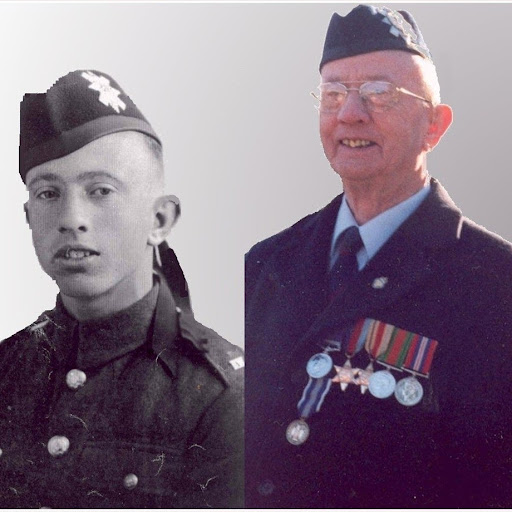

David J Tsgt Usafr A Hutton

view sourceIsbn (Books And Publications)

The Change Agent's Handbook: A Survival Guide for Quality Improvement Champions

view sourceAuthor

David W. Hutton

ISBN #

0873892879

From Baldrige to the Bottom Line: A Road Map for Organizational Change and Improvement

view sourceAuthor

David W. Hutton

ISBN #

0873894731

Lawyers & Attorneys

David Watson Hutton - Lawyer

view sourceLicenses:

Texas - Eligible To Practice In Texas 1992

Education:

California Western School of L

Degree - Doctor of Jurisprudence/Juris Doctor (J.D.)

Graduated - 1983

Degree - Doctor of Jurisprudence/Juris Doctor (J.D.)

Graduated - 1983

Specialties:

Government - 100%

Languages:

Arabic

Hindi

Indonesian

Mandarin

Hindi

Indonesian

Mandarin

David Hutton - Lawyer

view sourceSpecialties:

Corporate Law

Business Law

Taxation

Probate

Wills

Business Law

Taxation

Probate

Wills

ISLN:

906277926

Admitted:

1971

University:

St. Cloud State College, B.A., 1966

Law School:

William Mitchell College of Law, J.D., 1971; William Mitchell College of Law, LL.M., 1989

David Hutton - Lawyer

view sourceOffice:

Hutton & Associates, P.C.

Specialties:

Creditor Bankruptcy

Real Estate

Collections

Bank Foreclosures

Family Law

General Practice

Real Estate

Collections

Bank Foreclosures

Family Law

General Practice

ISLN:

906277919

Admitted:

1979

University:

Western Maryland College, B.A., 1976

Law School:

Washington & Lee University, J.D., 1979

Us Patents

-

Modular Binary Multiplier For Signed And Unsigned Operands Of Variable Widths

view source -

US Patent:7266580, Sep 4, 2007

-

Filed:May 12, 2003

-

Appl. No.:10/435976

-

Inventors:Fadi Y. Busaba - Poughkeepsie NY, US

Steven R. Carlough - Poughkeepsie NY, US

David S. Hutton - Poughkeepsie NY, US

Christopher A. Krygowski - Lagrangeville NY, US

Sheryll H. Veneracion - Poughkeepsie NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 7/52

-

US Classification:708625, 708628

-

Abstract:A method and apparatuses for performing binary multiplication on signed and unsigned operands of various lengths is discussed herein. It is a concept that may be split into two parts, the first of which is the multiplication hardware itself, a compact, less than-full sized multiplier employing Booth or other type of recoding methods upon the multiplier to reduce the number of partial products per scan, and implemented in such a manner so that a multiplication operation with large operands may be broken into subgroups of operations that will fit into this mid-sized multiplier whose results, here called modular products, may be knitted back together to form a correct, final product. The second part of the concept is the supporting hardware used to separate the operands into subgroups and input the data and control signals to the multiplier, and the algorithms and apparatuses used to align and combine the modular products properly to obtain the final product. These algorithms used to obtain a result as specified by the operation may be as varied as the supporting hardware with which the multiplier may be used, making this multiplier a very flexible and powerful design.

-

Separate Data And Coherency Cache Directories In A Shared Cache In A Multiprocessor System

view source -

US Patent:7475193, Jan 6, 2009

-

Filed:Jan 18, 2006

-

Appl. No.:11/334280

-

Inventors:David S. Hutton - Poughkeepsie NY, US

Kathryn M. Jackson - Poughkeepsie NY, US

Keith N. Langston - Woodstock NY, US

Pak-kin Mak - Poughkeepsie NY, US

Bruce Wagar - Tempe AZ, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/00

-

US Classification:711130, 711122

-

Abstract:A dual system shared cache directory structure for a cache memory performs the role of an inclusive shared system cache, i. e. , data, and system control, i. e. , coherency. The system includes two separate system cache directories in the shared system cache. The two separate cache directories are substantially equal in size and collectively large enough to contain all of the processor cache directory entries, but with only one of these separate cache directories hosting system-cache data to back the most recent fraction of data accessed by the processors. The other cache directory retains only addresses, including addresses of lines LRUed out from the first cache directory and the identity of the processor using the data. Thus by this expedient, only the directory known to be backed by system cached data will be evaluated for system cache memory data.

-

Modular Binary Multiplier For Signed And Unsigned Operands Of Variable Widths

view source -

US Patent:7490121, Feb 10, 2009

-

Filed:May 16, 2007

-

Appl. No.:11/749239

-

Inventors:Fadi Y. Busaba - Poughkeepsie NY, US

Steven R. Carlough - Poughkeepsie NY, US

David S. Hutton - Poughkeepsie NY, US

Christopher A. Krygowski - LaGrangeville NY, US

Sheryll H. Veneracion - Poughkeepsie NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 7/52

-

US Classification:708625

-

Abstract:A method of implementing binary multiplication in a processing device includes obtaining a multiplicand and a multiplier from a storage device; in the event the multiplier is larger than a selected length, partitioning the multiplier into a plurality of multiplier subgroups; in the event the multiplicand is larger than a selected length, partitioning the multiplicand into a plurality of multiplicand subgroups and at least one of zeroing out of unused bits of the multiplicand subgroup and sign-extending a smaller portion of the multiplicand subgroup; establishing a plurality of multiplicand multiples based on at least one of a selected multiplicand subgroup of the plurality of multiplicand subgroups and the multiplicand; selecting one or more of the multiplicand multiples of the plurality of multiplicand multiples based on the each multiplier subgroup of the plurality of multiplier subgroups; and generating a first modular product based on the selected multiplicand multiples.

-

Disowning Cache Entries On Aging Out Of The Entry

view source -

US Patent:7577795, Aug 18, 2009

-

Filed:Jan 25, 2006

-

Appl. No.:11/339196

-

Inventors:David S. Hutton - Poughkeepsie NY, US

Kathryn M. Jackson - Poughkeepsie NY, US

Keith N. Langston - Woodstock NY, US

Pak-kin Mak - Poughkeepsie NY, US

Chung-Lung K. Shum - Wappingers Falls NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/00

-

US Classification:711141, 711118, 711119, 711144, 711146

-

Abstract:Portions of data in a processor system are stored in a slower main memory and are transferred to a faster memory comprising a hierarchy of cache structures between one or more processors and the main memory. For a system with shared L2 cache(s) between the processor(s) and the main memory, an individual L1 cache of a processor must first communicate to an associated L2 cache(s), or check with such L2 cache(s), to obtain a copy of a particular line from a given cache location prior to, or upon modification, or appropriation of data at a given cached location. The individual L1 cache further includes provisions for notifying the L2 cache(s) upon determining when the data stored in the particular cache line in the L1 cache has been replaced, and when the particular cache line is disowned by an L1 cache, the L2 cache is updated to change the state of the particular cache line therein from an ownership state of exclusive to a particular identified CPU to an ownership state of exclusive to no CPU, thereby allowing reduction of cross interrogate delays during another processor acquisition of the same cache line.

-

Modular Binary Multiplier For Signed And Unsigned Operands Of Variable Widths

view source -

US Patent:7853635, Dec 14, 2010

-

Filed:May 16, 2007

-

Appl. No.:11/749224

-

Inventors:Fadi Y. Busaba - Poughkeepsie NY, US

Steven R. Carlough - Poughkeepsie NY, US

David S. Hutton - Poughkeepsie NY, US

Christopher A. Krygowski - LaGrangeville NY, US

Sheryll H. Veneracion - Poughkeepsie NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 7/38

G06F 7/52 -

US Classification:708524, 708625

-

Abstract:A system for binary multiplication in a superscalar processor includes a first pipeline, an execution unit, and a first multiplexer; a first rotator in communication with one register of the first pipeline and the execution unit; and a leading zero detection register in communication with the execution unit and another register of the first pipeline; a second pipeline, a second execution unit, and a second multiplexer; a rotator in communication with one register of the second pipeline and the second execution unit; and a leading zero detection register in communication with the second execution unit and another register of the first pipeline; and a third pipeline, a binary multiplier in communication with a pair registers of the third pipeline; a general register; an operand buffer for obtaining first and second operands; and a bus for communication between the pipelines, the general register and the operand buffer.

-

Method, System, And Computer Program Product For Selectively Accelerating Early Instruction Processing

view source -

US Patent:7861064, Dec 28, 2010

-

Filed:Feb 26, 2008

-

Appl. No.:12/037861

-

Inventors:Khary J. Alexander - Poughkeepsie NY, US

Fadi Y. Busaba - Poughkeepsie NY, US

Bruce C. Giamei - Poughkeepsie NY, US

David S. Hutton - Tallahassee FL, US

Chung-Lung Kevin Shum - Wappingers Falls NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 9/34

G06F 9/38 -

US Classification:712214, 712219

-

Abstract:A method for selectively accelerating early instruction processing including receiving an instruction data that is normally processed in an execution stage of a processor pipeline, wherein a configuration of the instruction data allows a processing of the instruction data to be accelerated from the execution stage to an address generation stage that occurs earlier in the processor pipeline than the execution stage, determining whether the instruction data can be dispatched to the address generation stage to be processed without being delayed due to an unavailability of a processing resource needed for the processing of the instruction data in the address generation stage, dispatching the instruction data to be processed in the address generation stage if it can be dispatched without being delayed due to the unavailability of the processing resource, and dispatching the instruction data to be processed in the execution stage if it can not be dispatched without being delayed due to the unavailability of the processing resource, wherein the processing of the instruction data is selectively accelerated using an address generation interlock scheme. A corresponding system and computer program product.

-

Method And System For Early Instruction Text Based Operand Store Compare Reject Avoidance

view source -

US Patent:7975130, Jul 5, 2011

-

Filed:Feb 20, 2008

-

Appl. No.:12/034042

-

Inventors:Khary J. Alexander - Poughkeepsie NY, US

Fadi Y. Busada - Poughkeepsie NY, US

Bruce C. Giamei - Poughkeepsie NY, US

David S. Hutton - Tallahassee FL, US

Chung-Lung Kevin Shum - Wappingers Falls NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 9/312

-

US Classification:712225, 712219

-

Abstract:A method and system for early instruction text based operand store compare avoidance in a processor are provided. The system includes a processor pipeline for processing instruction text in an instruction stream, where the instruction text includes operand address information. The system also includes delay logic to monitor the instruction stream. The delay logic performs a method that includes detecting a load instruction following a store instruction in the instruction stream, comparing the operand address information of the store instruction with the load instruction. The method also includes delaying the load instruction in the processor pipeline in response to detecting a common field value between the operand address information of the store instruction and the load instruction.

-

Disowning Cache Entries On Aging Out Of The Entry

view source -

US Patent:8131945, Mar 6, 2012

-

Filed:May 5, 2009

-

Appl. No.:12/435468

-

Inventors:David S. Hutton - Poughkeepsie NY, US

Kathryn M. Jackson - Poughkeepsie NY, US

Keith N. Langston - Woodstock NY, US

Pak-kin Mak - Poughkeepsie NY, US

Chung-Lung K. Shum - Wappingers Falls NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 12/00

-

US Classification:711141, 711118, 711119, 711122, 711144, 711146

-

Abstract:Caching where portions of data are stored in slower main memory and are transferred to faster memory between one or more processors and the main memory. The cache is such that an individual cache system must communicate to other associated cache systems, or check with such cache systems, to determine if they contain a copy of a given cached location prior to or upon modification or appropriation of data at a given cached location. The cache further includes provisions for determining when the data stored in a particular memory location may be replaced.

Plaxo

David Hutton

view sourceCaliforniaPast: Client Services Manager at Printra (now PageDNA), Manager, Professional Services...

david hutton

view sourcebellingham,wa.owner at David Hutton Real Estate School

DAVID HUTTON

view sourceAustin, TexasDirector of Planning at City of Leander

David Hutton

view sourceHutton Associates, Walnut Creek, CA

David Hutton

view sourceCanton, Ohio

David Hutton

view sourceArchie

David Hutton

view sourceCox Communications

David Hutton

view sourceSt Lukes Hospital

News

Instead of just flattening the COVID-19 curve, can we 'crush' it?

view source- David Hutton, an associate professor of health management and policy at the University of Michigan School of Public Health, agreed that "to really 'defeat' this in the long term and get back to 'business as usual' we will need a highly effective treatment or a vaccine." Until the virus is totally

- Date: Apr 03, 2020

- Category: More news

- Source: Google

Haynes Academy for Advanced Studies in Metairie announces second-quarter ...

view source- Seventh grade: Alma Adoue, Sabah Bashi, Abigail Batten, Hope Bernier, Madeleine Bourgeois, Cadin Chung, Kali Dancisak, Amanda Duong, Alexandra Edwards, David Fried, Hannah Guichet, Justin Hugger, David Hutton, Lincoln Kamenides, Sophie Luketich, Megan Marsalone, Lisa Pham, Mary Ponti, Brynna Robert,

- Date: Jan 23, 2013

- Source: Google

Flickr

Myspace

Googleplus

David Hutton

Education:

American College

Tagline:

I love to meet people and make friends

David Hutton

Work:

Simmway - Director

David Hutton

Work:

GCP - Director Food & Beverage

David Hutton

Relationship:

Married

David Hutton

Tagline:

Business Comms Consultant - Cost Management Expert!!!

David Hutton

David Hutton

David Hutton

Classmates

David Hutton

view sourceSchools:

Fleetwood Park High School Surrey Saudi Arabia 2002-2006

Community:

David Car

David Foster (Hutton)

view sourceSchools:

Mahaffey High School Mahaffey PA 1996-2001

David Hutton

view sourceSchools:

Ottawa Hills High School Toledo OH 1999-2003

Community:

Herb Flint, Lenny Kendall

David Hutton

view sourceSchools:

Eastern State High School Charleston IL 1943-1951

Community:

Sandra Dunevant, Kimberlee Swartz, Shirley Moen

David Hutton

view sourceSchools:

Laura Haygood School Atlanta GA 1966-1970, Green Acres Elementary School Smyrna GA 1970-1972, Osborne Junior High School Marietta GA 1972-1975

Community:

Debra Kehler, Warren Mobbs, Lucy Spivey, Vina Walker

David Hutton

view sourceSchools:

Whiteland Community High School Whiteland IN 1981-1985

Community:

Sandra Jarvis, John Spurr

David Hutton

view sourceSchools:

Borrego Springs High School Borrego Springs CA 1971-1975

Community:

Marika Birdsell, Ismael Rodriguez, Laurie Reeves, Mike Mailberg, Terri Chao

David Hutton

view sourceSchools:

Perrin-Whitt Cisd High School Perrin TX 1984-1997

Community:

Cheryl Riggs, Stephanie Samaniego, Sharon Wilhelm

Youtube

David M. Hutton

view source

David John Hutton

view source

David Hutton

view source

David Hutton

view source

David John Hutton

view source

David James Hutton

view source

David J Hutton

view source

David Tony Hutton

view sourceGet Report for David E Hutton from Mansfield, MA, age ~56