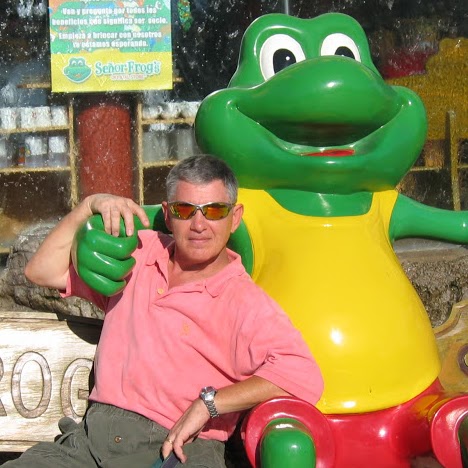

Ernest R Carter

age ~37

from Irving, TX

- Also known as:

-

- Ernest Ray Carter

- Ray Carter

Ernest Carter Phones & Addresses

- Irving, TX

- Austin, TX

- Round Rock, TX

- Rowlett, TX

- Cordova, TN

- Pflugerville, TX

- Memphis, TN

Wikipedia References

Ernest Carter (Drummer)

Us Patents

-

Incrementer With Common Precharge Enable And Carry-In Signal

view source -

US Patent:42187508, Aug 19, 1980

-

Filed:Sep 25, 1978

-

Appl. No.:5/945738

-

Inventors:Ernest A. Carter - Austin TX

Anthony E. Kouvoussis - Phoenix AZ -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G06F 748

H03K 2308 -

US Classification:364770

-

Abstract:A MOSFET incrementer circuit is disclosed which is adapted for use in conjunction with a clocked register for incrementing the binary value stored within the register. Each stage of the register has an input terminal which is used to determine whether or not the binary value stored in the particular stage is to be toggled. Each of the input terminals is precharged to a high level which corresponds to the no-increment mode of operation. After the input terminals are initially precharged, the input terminal of the least significant stage is driven to a low level to perform an increment. A plurality of series-coupled MOSFET devices are controlled according to output signals provided by each of the register stages for selectively coupling the low level present at the input terminal of the least significant stage to the input terminals of subsequent stages. When a low level is presented to the input terminal of a stage of the register, the binary value stored within the particular stage is toggled when the register is clocked, thereby causing the value stored within the register to be incremented. A common signal is used to initially precharge the voltage at each of the input terminals as well as to select an increment operation.

-

Series Read-Only-Memory Having Capacitive Bootstrap Precharging Circuitry

view source -

US Patent:45702390, Feb 11, 1986

-

Filed:Jan 24, 1983

-

Appl. No.:6/460335

-

Inventors:Ernest A. Carter - Austin TX

John K. Eitrheim - Austin TX

Dorothy M. Wood - Austin TX -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G11C 1140

G11C 1700 -

US Classification:365203

-

Abstract:A read-only-memory (ROM) having a plurality of enhancement and depletion transistors selectively arranged in an array with the gates of the transistors in each row connected in common to form word lines, and the current paths of the transistors in each column connected in series to form bit lines. The word lines are precharged and then allowed to float. The bit lines are then precharged, bootstrapping the word lines above the precharge level. A selected one of the word lines is thereafter discharged before one end of each of the bit lines is connected to ground. A selected bit line will either remain precharged or be discharged depending upon the type of transistor at the intersection of the selected word and bit lines.

-

Static Ram With Soft Defect Detection

view source -

US Patent:50349236, Jul 23, 1991

-

Filed:Dec 5, 1988

-

Appl. No.:7/283032

-

Inventors:Clinton C. K. Kuo - Austin TX

Ernest A. Carter - Austin TX -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G11C 11407

G11C 2900 -

US Classification:36518901

-

Abstract:A static RAM includes test features which provide for the detection of soft defects which may cause a defective SRAM cell to behave as a functional DRAM cell. Provision is made for writing either a high or a low logic state to each bit line of the SRAM while not writing any value to its complementary bit line and for sensing the state of each bit line independently of the state of its complementary bit line. In addition, a current test is provided which detects soft defects by means of the increased inverter leakage current caused thereby. It is possible, by properly combining these tests, to reliably detect all soft defects, thereby assuring the data retention capability of the SRAM. This technique avoids the long hold time and/or high temperature test techniques used in the prior art.

-

User Programmable Redundant Memory

view source -

US Patent:49758829, Dec 4, 1990

-

Filed:Oct 30, 1989

-

Appl. No.:7/429956

-

Inventors:Clinton C. K. Kuo - Austin TX

Ernest A. Carter - Austin TX

Joseph Jelemensky - Austin TX -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G11C 700

-

US Classification:365200

-

Abstract:A memory has a programmable circuit which allows a user to select an amount of redundancy the memory has varying from zero percent to one-hundred percent. A received address is compared by the circuit with a redundancy percentage control signal to determine if the address falls within a redundant portion of the memory. If so, a redundancy enable signal is asserted to allow the memory to utilize the redundant circuitry.

-

Analog To Digital Converter

view source -

US Patent:43814964, Apr 26, 1983

-

Filed:Nov 3, 1980

-

Appl. No.:6/202953

-

Inventors:Ernest A. Carter - Austin TX

-

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:H03K 1302

-

US Classification:340347AD

-

Abstract:A successive-approximation charge-redistribution analog-to-digital converter includes a binary weighted capacitive ladder for converting the least significant bits of the binary output representation and a resistive ladder for converting the higher order bits of the output representation. To achieve a half least significant bit shift, the capacitor of lowest capacitance in the ladder having a capacitance C is replaced by first and second capacitors each having a capacitance C/2. Each of these capacitors has a first terminal connected to the input of a comparator. Another input of the first capacitor is coupled to the low reference voltage. The second input of the second capacitor is coupled to one-eighth the high reference voltage during the sample phase and to the low reference voltage when the sample phase is completed. The resulting redistribution of charge which occurs at the input to the comparator is equivalent to minus one-half times the charge corresponding to one least significant bit. Thus, the stored sample to be converted is reduced in voltage by one-half least significant bit.

-

Mos Output Buffer With Reduced Supply Line Disturbance

view source -

US Patent:49595610, Sep 25, 1990

-

Filed:Mar 26, 1990

-

Appl. No.:7/499569

-

Inventors:Mark W. McDermott - Austin TX

Ernest A. Carter - Austin TX -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:H03K 1716

H03K 19017

H03K 512 -

US Classification:307443

-

Abstract:An output buffer with reduced supply line disturbance is provided for use in high performance microprocessor circuits. The output buffer uses a resistor and transistor as a sensing circuit, in parallel with an output driver transistor, thereby providing a negative feedback path into the control circuitry for the output driver. The sensing circuit detects the strength of the output driver transistor, by monitoring the amount of capacitance on the output node when the output buffer is driving the output signal to a logic high or logic low state, and rapidly produces a control voltage. The current flowing through the driver transistor and the sensor transistor causes a voltage drop across the resistor, which is fedback into the control circuitry. The control voltage is fed back into the output buffer control circuitry, thereby facilitating the reduction of the current drive capabilities of the driver and sensor transistors. Thus, the control circuitry reduces the change in current flow (di/dt) attributable to the operation of the driver and sensor transistors during the output buffer logic state transition.

-

Static Ram With Test Features

view source -

US Patent:54285747, Jun 27, 1995

-

Filed:Mar 28, 1991

-

Appl. No.:7/701536

-

Inventors:Clinton C. K. Kuo - Austin TX

Ernest A. Carter - Austin TX -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G11C 706

-

US Classification:365201

-

Abstract:A static RAM includes test features which provide for the detection of soft defects which may cause a defective SRAM cell to behave as a functional DRAM cell. Provision is made for writing either a high or a low logic state to each bit line of the SRAM while not writing any value to its complementary bit line and for sensing the state of each bit line independently of the state of its complementary bit line. In addition, a current test is provided which detects soft defects by means of the increased inverter leakage current caused thereby. It is possible, by properly combining these tests, to reliably detect all soft defects, thereby assuring the data retention capability of the SRAM. This technique avoids the long hold time and/or high temperature test techniques used in the prior art.

-

Bus Driver/Latch With Second Stage Stack Input

view source -

US Patent:42163897, Aug 5, 1980

-

Filed:Sep 25, 1978

-

Appl. No.:5/945740

-

Inventors:Ernest A. Carter - Austin TX

-

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:H03K 3281

H03K 3353 -

US Classification:307247R

-

Abstract:A latching circuit is disclosed having series connected first and second stage MOSFET devices within a first inverter circuit. An output signal provided at the upper node of the series connected devices is coupled by a feedback MOSFET to the input of a second MOSFET inverter. The output of the second MOSFET inverter is coupled to the gate of the first series connected MOSFET device while the input signal to be latched is coupled to the gate of the second of the series connected MOSFET devices. The lower output node of the series connected MOSFET devices is used to provide an output signal to a data bus so that the logic state stored by the latching circuit can be accessed. The latching circuit is controlled by timing signals such that the output signal provided by the lower node is in the proper logic state whenever the latching circuit is to be coupled to the data bus.

Name / Title

Company / Classification

Phones & Addresses

Baker, Jones, Daly & Carter P.A.

Attorneys & Lawyers - Real Estate

Attorneys & Lawyers - Real Estate

304 West Sunset Street, PO Box 986, Ahoskie, NC 27910

2523322181

2523322181

Director , Vice-President

THE HOLY ASSEMBLY OF JESUS CHRIST

110 Lone Star Blvd, Hutto, TX 78634

Director, Producer

NOBLE RECORDINGS, LLC

7105 Chiesa Rd, Rowlett, TX 75089

CARMAN INVESTMENT PROPERTIES, LLC

License Records

Ernest Waverly Carter Jr

License #:

2705075929

Category:

Contractor

Ernest J Carter

License #:

5786 - Expired

Category:

Pharmacy

Issued Date:

Jul 1, 1928

Effective Date:

Feb 20, 1974

Type:

Pharmacist

Resumes

Ernest Carter

view sourceLocation:

United States

President At Carter Technologies Co

view sourceLocation:

United States

Industry:

Environmental Services

Isbn (Books And Publications)

Britain's Railway Liveries: Colours, Crests, and Linings, 1825-1948

view sourceAuthor

Ernest Frank Carter

ISBN #

0287669890

Classmates

Ernest Carter

view sourceSchools:

Alabama School for the Deaf Talladega AL 1987-1991

Community:

Veronica Jones, Jimmy Phillips, Carl Wright, Rosie Rieves

Ernest Carter

view sourceSchools:

Alabama School for the Deaf Talladega AL 1980-1984

Community:

Veronica Jones, Jimmy Phillips, Carl Wright, Rosie Rieves

Ernest Carter

view sourceSchools:

Alabama School for the Deaf Talladega AL 1986-1990

Community:

Veronica Jones, Jimmy Phillips, Carl Wright, Rosie Rieves

Ernest Carter

view sourceSchools:

Alabama School for the Deaf Talladega AL 1986-1990

Community:

Veronica Jones, Jimmy Phillips, Carl Wright, Rosie Rieves

Ernest Carter

view sourceSchools:

Oak Grove Elementary School Atlanta GA 1989-1993, Miller Grove Junior High School Stone Mountain GA 1996-1998

Community:

Ricky Hinton, Tracie Everett, Tim Ramey, Clolita Castleberry

Ernest Williams (Carter)

view sourceSchools:

Sarah T. Reed Sr High School New Orleans LA 1987-1991

Community:

Latasha Lawton, Noni Marks

Ernest Carter

view sourceSchools:

Kentwood High School Kentwood LA 1994-1998

Community:

Georgie Corkern, Lydia Hackett

Ernest Carter

view sourceSchools:

Truman High School Taylor MI 1976-1980

Community:

Mike Macbrien, Steve Beals, Scott Langley

Ernest M Carter

view source

Ernest Carter

view source

Ernest Carter

view source

Ernest Carter

view source

Ernest Carter

view source

Ernest Carter

view source

Ernest Carter

view source

Ernest Carter

view sourceMyspace

Youtube

Flickr

Googleplus

Ernest Carter

Education:

Northeastern University - Mechanical Engineering

Ernest Carter

Ernest Carter

Tagline:

Thank God I'm a Country Boy

Ernest Carter

Ernest Carter

Ernest Carter

Ernest Carter

Ernest Carter

News

Maryland passes 2,000 COVID-19 hospitalizations

view source- Prince Georges County Health Officer Dr. Ernest Carter announced that the number of people hospitalized with COVID-19 in the county increased 27% since last week, reaching over 200 patients on Monday for the first time since February.

- Date: Dec 29, 2021

- Category: More news

- Source: Google

COVID-19 vaccine appointments in Prince George’s Co. after Feb. 9 to be ‘reset’

view source- We intend to make sure [vaccine distribution] is equitable, Health Officer Dr. Ernest Carter said, while County Executive Angela Alsobrooks added, We want people who are living here and working here to get their vaccinations here.

- Date: Jan 19, 2021

- Category: More news

- Source: Google

Prince George’s Co. to shut down indoor dining amid rise in coronavirus cases

view source- On Nov. 8, there were 68 people hospitalized in the county with COVID-19. By Dec. 8, that had more than doubled to 177 and is continuing to rise, Prince Georges County Health Officer Dr. Ernest Carter said.

- Date: Dec 10, 2020

- Category: More news

- Source: Google

Plaxo

Ernest Carter

view sourceLadera Ranch, CARealtor at ALTERA REAL ESTATE

Ernest Carter

view sourceGet Report for Ernest R Carter from Irving, TX, age ~37