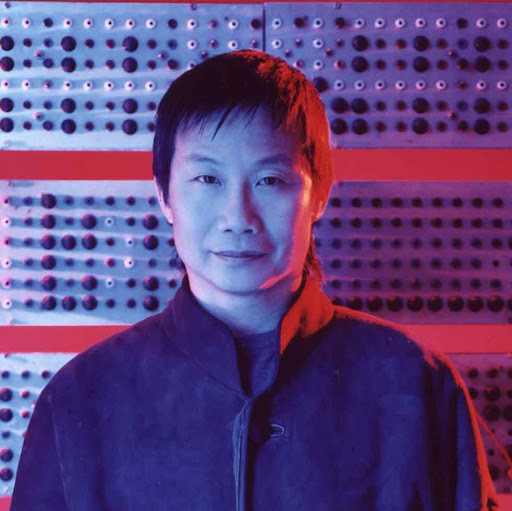

Gary T Chang

age ~60

from Rowland Heights, CA

- Also known as:

-

- Gary Te Chang

- Gary C Chang

- Gary King

Gary Chang Phones & Addresses

- Rowland Heights, CA

- Los Altos, CA

- Cupertino, CA

- Alhambra, CA

- West Covina, CA

- San Jose, CA

- Sunnyvale, CA

- Rowland Heights, CA

- Santa Clara, CA

- Los Angeles, CA

- Palo Alto, CA

Lawyers & Attorneys

Gary Kao-Ning Chang - Lawyer

view sourceLicenses:

California - Active 2005

Education:

University of California - Berkeley

University of California, Hastings College of the Law

University of California, Hastings College of the Law

Gary Mark Chang, Los Angeles CA - Lawyer

view sourceAddress:

Law Ofc Gary M Chang

330 E 2Nd St Ste 201B, Los Angeles, CA 90012

2139255526 (Office)

330 E 2Nd St Ste 201B, Los Angeles, CA 90012

2139255526 (Office)

Licenses:

California - Active 1998

Education:

Southwestern University School of Law

University of California at Los Angeles School of Law

University of California at Los Angeles School of Law

Gary Chang - Lawyer

view sourceOffice:

Law Office of Gary M. Chang

ISLN:

913912964

Admitted:

1998

University:

University of California at Los Angeles, B.A.

Law School:

Southwestern University School of Law, J.D., 1997

Name / Title

Company / Classification

Phones & Addresses

Executive Officer

Oakland Board of Realtors

Oakland Association of Realtors

Business & Trade Organizations

Oakland Association of Realtors

Business & Trade Organizations

1528 Webster St, Oakland, CA 94612

5108363000, 5102720661

5108363000, 5102720661

President

U S Colo, LLC

Miscellaneous Retail Stores

Miscellaneous Retail Stores

650 S Grand Ave Ste 1000, Los Angeles, CA 90017

Attorney

Connor & Bishop

Legal Services

Legal Services

120 Montgomery St, San Francisco, CA 94104

Vice President

Raycon

Roofing, Siding, and Insulation Materials

Roofing, Siding, and Insulation Materials

2010 Hartog Dr, San Jose, CA 95131

Manager

Mobile Stereotactic Surgical Systems

Offices and Clinics of Doctors of Medicine

Offices and Clinics of Doctors of Medicine

2811 Wilshire Blvd Ste 810, Santa Monica, CA 90403

Executive

Good Land International Co

Land, Mineral, Wildlife, and Forest Conservat...

Land, Mineral, Wildlife, and Forest Conservat...

328 Edgewater Dr, Los Gatos, CA 95033

Marketing Director

Tri Valley Internet

Telephone Communications, Except Radiotelephone

Telephone Communications, Except Radiotelephone

4713 1St St Ste 110, Pleasanton, CA 94566

Owner

Aqua Day Spa

Beauty Shops

Beauty Shops

1155 Oxford St, Berkeley, CA 94707

Wikipedia References

Gary Chang

Gary Chang (Architect)

Us Patents

-

Time Sharing A Single Port Memory Among A Plurality Of Ports

view source -

US Patent:6920510, Jul 19, 2005

-

Filed:Jun 5, 2002

-

Appl. No.:10/163047

-

Inventors:Gary Chang - San Jose CA, US

-

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G06F003/00

G06F003/06

G06F005/00 -

US Classification:710 36, 710 2, 710 22, 710 23, 710 28, 710 33, 710 37, 710 40, 710 45, 710 51, 710 52, 710 57, 709212, 709234

-

Abstract:An apparatus comprising a first circuit and a second circuit. The first circuit may be configured to transfer data between a plurality of first ports and a second port via a single port memory in response to one or more control signals. The second circuit may be configured to generate the one or more control signals, wherein the memory is time shared among the second port and the plurality of first ports.

-

Built-In Debug Feature For Complex Vlsi Chip

view source -

US Patent:7111199, Sep 19, 2006

-

Filed:Jul 8, 2002

-

Appl. No.:10/190933

-

Inventors:Ho-Ming Leung - Cupertino CA, US

Fan Zhang - San Jose CA, US

Gary Chang - San Jose CA, US -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:G06F 11/00

-

US Classification:714 30, 714733

-

Abstract:An apparatus comprising (i) a first circuit configured to generate one or more node signals at one or more internal nodes and (ii) a second circuit configured to present one or more of the node signals and a trigger signal in response to one or more control signals.

-

Efficient And High Speed 2D Data Transpose Engine For Soc Application

view source -

US Patent:7742063, Jun 22, 2010

-

Filed:Jul 7, 2005

-

Appl. No.:11/176040

-

Inventors:Ho-Ming Leung - Cupertino CA, US

Gary Chang - San Jose CA, US -

Assignee:LSI Corporation - Milpitas CA

-

International Classification:G09G 5/00

-

US Classification:345649, 345656, 345657, 345658, 345559

-

Abstract:An apparatus comprising a buffer circuit, a rotation circuit and a memory. The buffer may be configured to store original image data in one or more sub-matrices. The rotation circuit may be configured to (i) produce rotated data and (ii) store the rotated data in a transposed matrix. The memory may be configured to position the rotated data in the transposed matrix. The transposed matrix comprises final image data rotated by a predetermined angle from the original image data.

-

Integrated Circuit With On-Chip Clock Frequency Matching To Upstream Head End Equipment

view source -

US Patent:7362767, Apr 22, 2008

-

Filed:Jul 22, 2003

-

Appl. No.:10/624264

-

Inventors:Omer F. Orberk - Mountain View CA, US

Ho-Ming Leung - Cupertino CA, US

Gary Chang - San Jose CA, US -

Assignee:LSI Logic Corporation - Milpitas CA

-

International Classification:H04L 12/56

-

US Classification:37039562, 713400, 713401, 375356

-

Abstract:One aspect of the present invention concerns a method for controlling the frequency of oscillation of a local clock signal comprising the steps of (A) generating the clock signal in response to a first control signal, (B) generating the first control signal in response to one of a plurality of adjustment signals selected in response to a second control signal and (C) generating the second control signal in response to a comparison between a local timestamp and an external timestamp.

-

System And Method For Effectively Implementing A High-Speed Dram Device

view source -

US Patent:20040114420, Jun 17, 2004

-

Filed:Dec 16, 2002

-

Appl. No.:10/320056

-

Inventors:Kuoyuan Hsu - San Jose CA, US

Gary Chang - Saratoga CA, US

Patrick Chuang - Cupertino CA, US -

International Classification:G11C011/24

-

US Classification:365/149000

-

Abstract:A system and method for effectively implementing a high-speed DRAM device may include memory cells that each have a bitline for transferring storage data, a wordline for enabling an accelerated-write operation in the memory cell, and a data storage node with a corresponding cell voltage. An accelerated-write circuit may then directly provide the storage data to an appropriate bitline in a pre-toggled state in response to one or more accelerated-write enable signals. The corresponding cell voltage may therefore begin a state-change transition towards the pre-toggled state immediately after the wordline is activated to successfully reach a full-state level before the wordline is deactivated during a high-speed memory cycle.

-

On-Chip Pulse-Width Control Circuit For Sram Memories

view source -

US Patent:47697911, Sep 6, 1988

-

Filed:Aug 6, 1986

-

Appl. No.:6/894584

-

Inventors:May-Lin Lee - Cupertino CA

Moon S. Kok - Milpitas CA

Gary Chang - San Jose CA -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G11C 700

-

US Classification:365203

-

Abstract:The circuit provides one or several banks of capacitors, the capacitors in each bank being identical in size. A single fuse for each bank of capacitors controls the connection of the capacitors to a pulse-width-determining node on each of the ATD (address-transition-detect) pulse generators of the SRAM device. Depending on the position of the fuse in the circuit, the blowing of a single fuse can either add to the capacitance at the ATD nodes or substract from it. Thus the pulse-width of all ATD pulse generators can be adjusted shorter or longer simultaneously by blowing a single fuse only.

-

Method For Power Management And Power Management Controller For A Radio Receiver

view source -

US Patent:20170181219, Jun 22, 2017

-

Filed:Nov 16, 2016

-

Appl. No.:15/352896

-

Inventors:- Santa Clara CA, US

Ziljian Bai - Neubiberg, DE

Gary Chang - Santa Clara CA, US

Matthias Obermeier - Taufkirchen, DE

Mathias Kurth - Dresden, DE

Ismael Gutierrez - San Jose CA, US

Sven Dortmund - Essen, DE -

International Classification:H04W 76/04

H04W 52/02

H04B 17/336

H04W 72/04 -

Abstract:A method () for power management in a radio receiver includes: receiving () a sequence of radio subframes over a radio channel, each radio subframe comprising at least one control region and at least one data region; monitoring () control information from at least one control region of at least one radio subframe; generating () a channel metric based on the monitored control information, the channel metric indicating a quality of the radio channel; and selecting () a control region decoding mode based on the channel metric, the control region decoding mode indicating a scheduling for disabling reception of at least part of the at least one data region of the sequence of radio subframes.

Medicine Doctors

Gary J. Chang

view sourceSpecialties:

Anesthesiology, Pain Management

Work:

Monterey Peninsula Surgery Center

665 Munras Ave STE 100, Monterey, CA 93940

8316499300 (phone), 8313726152 (fax)

665 Munras Ave STE 100, Monterey, CA 93940

8316499300 (phone), 8313726152 (fax)

Education:

Medical School

Medical College of Wisconsin School of Medicine

Graduated: 1981

Medical College of Wisconsin School of Medicine

Graduated: 1981

Languages:

English

Spanish

Spanish

Description:

Dr. Chang graduated from the Medical College of Wisconsin School of Medicine in 1981. He works in Monterey, CA and specializes in Anesthesiology and Pain Management. Dr. Chang is affiliated with Community Hospital Of The Monterey Peninsula.

Gary John Chang, Monterey CA

view sourceSpecialties:

Anesthesiology

Pain Medicine

Pain Medicine

Pain Medicine

Pain Medicine

Work:

Monterey Spine & Joint

12 Upper Ragsdale Dr, Monterey, CA 93940

The Pain & Rehabilitation Medical Group

3445 Pacific Coast Hwy, Torrance, CA 90505

12 Upper Ragsdale Dr, Monterey, CA 93940

The Pain & Rehabilitation Medical Group

3445 Pacific Coast Hwy, Torrance, CA 90505

Education:

Medical College of Wisconsin (1981)

Googleplus

Gary Chang

Work:

Columbia College Chicago - Associate Professor - Film Music Composition

Education:

California Institute of the Arts - BFA Music Composition, California Institute of the Arts - MFA Music Composition

About:

Gary Chang

Tagline:

Film Music Composer

Bragging Rights:

I scored 8 films by John Frankenheimer.

Gary Chang

Work:

Weill Cornell Medical College - Training and Support Manager (2004)

Education:

New York University Stern School of Business - MBA, Cornell University - Computer Science

Gary Chang

Lived:

San Jose, CA

Hong Kong

Davis, CA

Hong Kong

Davis, CA

Education:

UC Davis - Managerial Economics

Gary Chang

Lived:

Pasadena, CA

Work:

BBC Worldwide - Senior Analyst

Education:

University of California, Los Angeles

Gary Chang (Pastor)

Work:

Chinese Bible Church of San Diego - Temecula Campus Pastor

Relationship:

Married

Gary Chang

Education:

University of California, Los Angeles - Computer Science

Gary Chang

Work:

Apollo Building Products

Gary Chang

Youtube

Classmates

Gary Chang

view sourceSchools:

Howell Middle School Victoria TX 1994-1998

Community:

Diana Malone, Russell Janecka, Sherrie Calvert

Gary Chang

view sourceSchools:

LeMoyne School Chicago IL 1974-1978

Community:

Sandra Young, Jackie Spicuzza, Pam Scoggins, Sarah Williams

LeMoyne School, Chicago, ...

view sourceGraduates:

Gary Chang (1974-1978),

Jodi Bozzelli (1967-1969),

Howard Rubenstein (1943-1945),

Christina Judnich (1956-1958)

Jodi Bozzelli (1967-1969),

Howard Rubenstein (1943-1945),

Christina Judnich (1956-1958)

Chang Gary

view source

Gary Chang

view source

Gary Chang Foo Heng

view source

Gary Chang

view source

Gary Chang

view source

Gary Chang

view source

Gary Chang

view source

Gary Chang

view sourceFlickr

Plaxo

Gary Chang

view sourceBroadcom Corporation

gary chang

view sourcePresident at MBC

Get Report for Gary T Chang from Rowland Heights, CA, age ~60