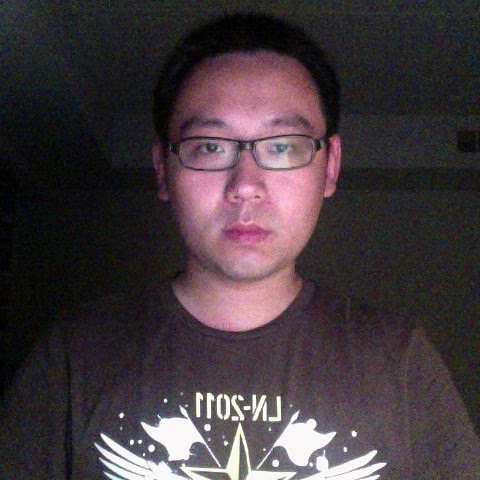

Jiong Zhang

from Alhambra, CA

- Also known as:

-

- Jing Zhang

- Jiong Zheng

- Jiong Zhan

- Phone and address:

-

428 Monterey St, Alhambra, CA 91801

6264579382

Jiong Zhang Phones & Addresses

- 428 Monterey St, Alhambra, CA 91801 • 6264579382

- 805 Chapel Ave, Alhambra, CA 91801 • 6268720025

- 111 Curtis Ave, Alhambra, CA 91801 • 6264579382

- San Gabriel, CA

- Baldwin Park, CA

- Baldwin Park, CA

Resumes

Sr. Principal, Scientist At Broadcom Corp.

view sourcePosition:

Sr. Principal, Scientist at Broadcom Corp.

Location:

Orange County, California Area

Industry:

Semiconductors

Work:

Broadcom Corp. since Jan 2007

Sr. Principal, Scientist

Skyworks Solutions Inc. Jun 2002 - Dec 2007

Principal Engineer

Conexant Systems Inc. Apr 2002 - Jun 2002

Senior Staff Engineer

Chartered Semiconductor MFG. Apr 1999 - Mar 2002

Senior Engineer

Sr. Principal, Scientist

Skyworks Solutions Inc. Jun 2002 - Dec 2007

Principal Engineer

Conexant Systems Inc. Apr 2002 - Jun 2002

Senior Staff Engineer

Chartered Semiconductor MFG. Apr 1999 - Mar 2002

Senior Engineer

Education:

Tsinghua University 1994 - 1999

Ph.D, Microelectronics

Ph.D, Microelectronics

Jiong Zhang

view source

Jiong Zhang

view source

Jiong Zhang

view sourceUs Patents

-

Esd Protection Structure Using Contact-Via Chains As Ballast Resistors

view source -

US Patent:7397089, Jul 8, 2008

-

Filed:Aug 10, 2005

-

Appl. No.:11/201638

-

Inventors:Jiong Zhang - Irvine CA, US

Yuhua Cheng - Irvine CA, US -

Assignee:Skyworks Solutions, Inc. - Woburn MA

-

International Classification:H01L 23/62

-

US Classification:257360, 257355

-

Abstract:According to an exemplary embodiment, an ESD protection structure situated in a semiconductor die includes a FET including a gate and first and second active regions, where the gate includes at least one gate finger, and where the at least one gate finger is situated between the first and second active regions. The ESD protection structure further includes at least one contact-via chain connected to the first active region, where the at least one contact-via chain includes a contact connected to a via. The at least one contact-via chain forms a ballast resistor for increased ESD current distribution uniformity. The contact is connected to the via by a first metal segment situated in a first interconnect metal layer of a die. The at least one contact-via chain is connected between the first active region and a second metal segment situated in a second interconnect metal layer of the die.

-

Power Clamp For On-Chip Esd Protection

view source -

US Patent:20090040671, Feb 12, 2009

-

Filed:Aug 1, 2008

-

Appl. No.:12/221286

-

Inventors:Jiong Zhang - Irvine CA, US

-

Assignee:SKYWORKS SOLUTIONS, INC. - WOBURN MA

-

International Classification:H02H 9/04

-

US Classification:361 56

-

Abstract:According to an exemplary embodiment, a power clamp for providing on-chip ESD and mistrigger event protection includes a clamping transistor coupled between a power bus and a ground. The power clamp further includes a number of inverter stages coupled in series, where a first inverter stage has an output coupled to the clamping transistor. The power clamp further includes a turn-off resistor coupled between the power bus and an input of the first inverter. The turn-off resistor is configured to cause the clamping transistor to automatically turn off after having been turned on. The turn-off resistor determines a period of time that the clamping transistor is turned on after an ESD or mistrigger event has occurred on the power bus. The power clamp further includes a timing circuit coupled to the inverter stages. The power clamp further includes a feedback transistor coupled between a second inverter stage and the power bus.

-

Metal-Oxide-Metal Capacitor

view source -

US Patent:20130342955, Dec 26, 2013

-

Filed:Jun 26, 2012

-

Appl. No.:13/533280

-

Inventors:Jiong Zhang - Irvine CA, US

Joseph King - Aliso Viejo CA, US

Akira Ito - Irvine CA, US -

Assignee:Broadcom Corporation - Irvine CA

-

International Classification:H01G 4/002

H01G 4/00 -

US Classification:3613011, 29 2503

-

Abstract:A semiconductor structure may implement a metal-oxide-metal capacitor. When layer design rules change from one layer to the next, the structure may change the direction of the interleaved plates of the capacitor. For example, when the metallization width or spacing design rules change from layer M3 to layer M4, the structure may run the capacitor traces in different directions (e.g., orthogonal to one another) on M3 as compared to M4. Among the layers that adhere to the same design rules, for example layers M1, M2, and M3, the structure may run the capacitor traces in the same direction in each of the layers M1, M2, and M3. In this way, the capacitor traces overlap to large extent without misalignment on layers that have the same design rules, and the structure avoids misalignment of the capacitor traces when the design rules change.

Medicine Doctors

Jiong Zhang

view sourceGoogleplus

Jiong Zhang

Education:

University of Pittsburgh - MSIS, University of Tasmania - Information Systems, Shanghai Ocean Univerisity - Management Information System

Jiong Zhang

Jiong Zhang

Jiong Zhang

Jiong Zhang

Jiong Zhang

Jiong Carol Zhang

view source

Jiong Zhang

view source

Jiong Zhang

view sourceClassmates

Jiong Zhang | Santa Monic...

view sourceYoutube

Flickr

Get Report for Jiong Zhang from Alhambra, CA