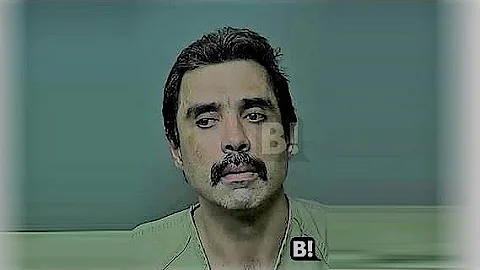

Joseph J Palumbo

age ~63

from Poughkeepsie, NY

- Also known as:

-

- Joe J Palumbo

- Joseph Palumbo Joseph

- Phone and address:

- 66 Round Hill Rd, Poughkeepsie, NY 12603

Joseph Palumbo Phones & Addresses

- 66 Round Hill Rd, Poughkeepsie, NY 12603

- 31 Talmadge St, Poughkeepsie, NY 12601

- 5 Wildwood Dr, Wappingers Falls, NY 12590

- Wappingers Fl, NY

- Kingston, NY

Work

-

Position:Sales Occupations

Education

-

Degree:High school graduate or higher

Emails

Lawyers & Attorneys

Joseph Palumbo - Lawyer

view sourceISLN:

1001076790

Admitted:

(Admission pending)

University:

Macaulay Honors College, B.A., 2016

Law School:

Cardozo Law School, J.D., 2020

Joseph Palumbo - Lawyer

view sourceOffice:

Gilmore & Bell A Professional Corporation

Specialties:

Infrastructure/Municipal Facilities

Economic Development

K-12 Education

Family

Higher Education

Water, Sewer & Gas Utilities

Manufacturing Facilities

Economic Development

K-12 Education

Family

Higher Education

Water, Sewer & Gas Utilities

Manufacturing Facilities

ISLN:

923455666

Admitted:

2013

University:

Quincy University, B.S., 2008

Law School:

University of Missouri, J.D., 2013

Name / Title

Company / Classification

Phones & Addresses

President

Hurricane Shutters of South Florida, Inc

Robert G. Franklin. Inc.

Shutters

Robert G. Franklin. Inc.

Shutters

870 Old Dixie Hwy, Bay 16-17, Lake Park, FL 33403

5613391837, 5617480059

5613391837, 5617480059

President

Joe's Auto Repair Inc

General Auto Repair · Auto Repair

General Auto Repair · Auto Repair

81 Old Manorton Rd, Taghkanic, NY 12523

83 Old Manorton Rd, Elizaville, NY 12523

5185376000

83 Old Manorton Rd, Elizaville, NY 12523

5185376000

JOSEPH M. PALUMBO, DO, LLC

GREEN MOUNTAIN AGENCY, INC

Insurance Agent/Broker

Insurance Agent/Broker

815 Blooming Grv Tpke STE 3, New Windsor, NY 12553

PO Box 4470, New Windsor, NY 12553

PO Box 4470, New Windsor, NY 12553

Us Patents

-

Method For Identification And Removal Of Non-Timing Critical Wire Routes From Congestion Region

view source -

US Patent:6904585, Jun 7, 2005

-

Filed:Apr 4, 2003

-

Appl. No.:10/408206

-

Inventors:Mark A. Brittain - Pflugerville TX, US

Kenneth D. Klapproth - Austin TX, US

Vu T. Le - Poughkeepsie NY, US

Joseph J. Palumbo - Poughkeepsie NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F017/50

-

US Classification:716 13, 716 12, 716 14, 716 5

-

Abstract:A method for identifying and modifying, in a VLSI chip design, wire routes within a region of wiring congestion that can be routed around that region without inducing timing violations by the insertion and proper placement of inverters. Circuits and nets are examined in the vicinity of the wiring congestion to determine those nets with high potential to drive a route outside the region. Circuit locations are analyzed to determine if the net connecting them creates a path through the region of wiring congestion. Timing slacks are derived from the timing reports for such nets and compared against a timing value representing the additional delay of using an inverter pair to drive the wire route outside the region of wiring congestion. If a net has sufficient timing slack, it is buffered with an inverter pair which is then placed in a manner as to force the wire routes for the modified path around the region of wiring congestion, thereby reducing the wire utilization within the region.

-

Method For Identification Of Sub-Optimally Placed Circuits

view source -

US Patent:6990648, Jan 24, 2006

-

Filed:Apr 4, 2003

-

Appl. No.:10/408203

-

Inventors:Joseph J. Palumbo - Poughkeepsie NY, US

-

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 17/50

-

US Classification:716 9, 716 10, 716 5, 716 7, 716 2

-

Abstract:A method for identifying, in a VLSI chip design, circuits placed in an region of wiring congestion which can be replaced such that wiring tracks are freed up due to decreased net lengths without any pin to pin segment increasing in length. Circuits placed within the region of wiring congestion are identified and examined to determine the circuits they connect to. The placements of the connected circuits are analyzed to derive a rectangle of connectivity. Each of the originally identified circuits are then checked to determine if they are placed within their associated rectangle of connectivity. If not, the distance between the circuit and rectangle is calculated along with a recommended placement location, both of which are reported along with the circuit. The recommended placement location is a point along the border of the rectangle such that replacement of the circuit at the location reduces all circuit net lengths without increasing any pin to pin segment. In this way, wiring tracks are freed up without any potential for increased path delays.

-

Method, System, And Computer Program Product For Hierarchical Integrated Circuit Repartitioning

view source -

US Patent:7568176, Jul 28, 2009

-

Filed:Jun 4, 2007

-

Appl. No.:11/757457

-

Inventors:Adam R. Jatkowski - Wyoming PA, US

Joseph J. Palumbo - Poughkeepsie NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 17/50

-

US Classification:716 7, 716 8

-

Abstract:A method, system, and computer program product for hierarchical integrated circuit repartitioning are provided. The method includes receiving parent level placement data for one or more interconnecting elements and designating at least one child to receive a pushdown of the one or more interconnecting elements from the parent level. For each child designated to receive the pushdown of the one or more interconnecting elements, the method further includes determining a physical coverage area of the child, identifying which of the one or more interconnecting elements within the physical coverage area of the child to pushdown into the child, generating an interconnecting element pushdown list for the child, including wiring layer information, and outputting the interconnecting element pushdown list.

-

Buffer Placement With Respect To Data Flow Direction And Placement Area Geometry In Hierarchical Vls Designs

view source -

US Patent:7827513, Nov 2, 2010

-

Filed:Oct 11, 2007

-

Appl. No.:11/870728

-

Inventors:Joseph J. Palumbo - Poughkeepsie NY, US

Christopher J. Berry - Hudson NY, US

Adam R. Jalkowski - Wyoming PA, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 17/50

-

US Classification:716 10, 716 14

-

Abstract:A method for identifying and modifying, in a VLSI hierarchical chip design, parent buffer placements which lead to wiring track inefficiencies with respect to data flow and the parent placement area geometry. Parent placement area is reviewed and a subset is categorized and distinguished as either horizontal slots or vertical slots. Buffer to buffer data flow is reviewed for cases where data flow direction is either strongly horizontal or strongly vertical. Situations where buffer to buffer data flow is oriented in the same direction as the parent placement slots in which the buffers reside are reported. Additionally, an attempt is made to find a valid placement location for the buffers excluding parent placement areas oriented in the same direction as the data flow.

-

Automated Method For Buffering In A Vlsi Design

view source -

US Patent:8010922, Aug 30, 2011

-

Filed:Feb 18, 2008

-

Appl. No.:12/032762

-

Inventors:Frank Malgioglio - Hopewell Junction NY, US

Adam R. Jatkowski - Wyoming PA, US

Brian A. Lasseter - Austin TX, US

Joseph J. Palumbo - Poughkeepsie NY, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 17/50

-

US Classification:716114, 716113

-

Abstract:Buffers are placed on selected nets coupled to input and output pins of entities in an IC device. This includes loading selected input and output pins of entities prior to respectively buffering nets of the entities and buffering in successive iterations, which includes setting artificial loads on selected input pins. The buffering in a current iteration is limited to i) buffering nets on the current iteration entity for receivers on the current iteration entity and ii) buffering nets on the current iteration entity directly coupled to respective nets of an immediately adjacent entity that has been buffered already in a preceding one of iterations, but only if the already buffered net is coupled to a receiver on its own net or a receiver on some other already buffered net via nets that have all been buffered via one or more of the preceding iterations.

-

Designing A Robust Power Efficient Clock Distribution Network

view source -

US Patent:20130326456, Dec 5, 2013

-

Filed:Jun 4, 2012

-

Appl. No.:13/488065

-

Inventors:Charles Jay Alpert - Austin TX, US

Joseph Nicolas Kozhaya - Morrisville NC, US

Zhuo Li - Cedar Park TX, US

Joseph J Palumbo - Poughkeepsie NY, US

Haifeng Qian - White Plains NY, US

Phillip John Restle - Katonah NY, US

Chin Ngai Sze - Austin TX, US

Ying Zhou - , US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 17/50

-

US Classification:716122

-

Abstract:An electronic automation design tool with a sink locator unit creates clusters of loads from a plurality of loads within a sector of a clock network design based on balancing magnitudes of the loads among the clusters of loads and based on minimal delays of each of the clusters and respective ones of a plurality of sink locations in the sector of the clock network design. The tool determines centers of the clusters of loads, and sink locations corresponding to the centers of the clusters for connecting output terminal points of sector buffers are determined. Each of the sector buffers drive a clock signal to a corresponding one of the clusters of loads.

-

Data Processing System To Implement Wiring/Silicon Blockages Via Parameterized Cells

view source -

US Patent:20180232481, Aug 16, 2018

-

Filed:Feb 13, 2017

-

Appl. No.:15/431061

-

Inventors:- Armonk NY, US

Adam R. Jatkowski - Wyoming PA, US

Frank Malgioglio - Hopewell Junction NY, US

Ryan M. Nett - Austin TX, US

Joseph J. Palumbo - Poughkeepsie NY, US

Sean Salisbury - Poughkeepsie NY, US -

International Classification:G06F 17/50

-

Abstract:A data processing system to implement wiring/silicon blockages via parameterized cells (pCells) includes a front end-of-line placement/blockage (FEOL P/B) controller to generate a placement blockage based on an input parameter corresponding to a physical design of an integrated circuit (IC). The FEOL P/B outputs a placement blockage parameter that is stored in a wire track allocation database to indicate the placement blockage. A back end-of-line wiring track (BEOL WT) controller generates a wire track blockage of the IC. A BEOL power track (BEOL PT) controller generates a metal blockage within the wire track blockage. A combination of the metal blockage and the wire track blockage defines a parent-child contract to enable concurrent physical design of the IC without creating shorts and overlaps in a child block of the IC.

-

Constraint-Driven Pin Optimization For Hierarchical Design Convergence

view source -

US Patent:20170132349, May 11, 2017

-

Filed:Nov 10, 2015

-

Appl. No.:14/936920

-

Inventors:- Armonk NY, US

Randall J. Darden - Ridgedale MO, US

Adam R. Jatkowski - Bethlehem PA, US

Joseph J. Palumbo - Poughkeepsie NY, US

Shyam Ramji - Lagrangeville NY, US

Sourav Saha - Barrackpur, IN

Timothy A. Schell - San Diego CA, US

Eddy St. Juste - Bridgeport CT, US -

International Classification:G06F 17/50

-

Abstract:A computer-implemented method of performing physical synthesis in a chip design process using hierarchical wire-pin co-optimization, a system, and a computer program product are described. Aspects include providing an indication of candidate pins among a plurality of pins of a plurality of macros that may be moved, and providing constraints on a range of movement of one or more of the plurality of pins. Aspects also include performing macro-level physical synthesis at each of the plurality of macros based on the candidate pins and the constraints to generate pin locations and timing results.

Medicine Doctors

Joseph S. Palumbo

view sourceSpecialties:

Pediatric Hematology-Oncology

Work:

Cincinnati Childrens Hospital Cancer & Blood Disease Institute

3333 Burnet Ave Ml2011, Cincinnati, OH 45229

5136364266 (phone), 5136363220 (fax)

Cincinnati Childrens Hospital Hematology

3333 Burnet Ave Mlc 7015, Cincinnati, OH 45229

5136364269 (phone)

3333 Burnet Ave Ml2011, Cincinnati, OH 45229

5136364266 (phone), 5136363220 (fax)

Cincinnati Childrens Hospital Hematology

3333 Burnet Ave Mlc 7015, Cincinnati, OH 45229

5136364269 (phone)

Education:

Medical School

Pennsylvania State University College of Medicine

Graduated: 1993

Pennsylvania State University College of Medicine

Graduated: 1993

Procedures:

Bone Marrow Biopsy

Chemotherapy

Chemotherapy

Conditions:

Hemolytic Anemia

Sickle-Cell Disease

Anemia

Hemophilia A or B

Iron Deficiency Anemia

Sickle-Cell Disease

Anemia

Hemophilia A or B

Iron Deficiency Anemia

Languages:

English

Spanish

Spanish

Description:

Dr. Palumbo graduated from the Pennsylvania State University College of Medicine in 1993. He works in Cincinnati, OH and 1 other location and specializes in Pediatric Hematology-Oncology. Dr. Palumbo is affiliated with Cincinnati Childrens Hospital Medical Center.

Classmates

Joseph Palumbo

view sourceSchools:

Monaca High School Monaca PA 1941-1945

Community:

Sandra Osburn, Lawrence Terry, David Bradel, Debbie Mcmahon, John Tozana

Joseph Palumbo

view sourceSchools:

Stamford Adult Education High School Stamford CT 1976-1980

Community:

Renee Webster

Joseph Palumbo

view sourceSchools:

Corpus Christi Parochial School Philadelphia PA 1948-1952

Community:

Joseph Wright, Thomas Collier, Martin Heenan, Joan Lentz, Maryanne Zimmerman

Joseph Palumbo

view sourceSchools:

Wardlaw-Hartridge High School Edison NJ 1992-1996

Community:

Eric Eckert, Lee Berg, Lon Berg, Fred Scheer

Joseph Palumbo

view sourceSchools:

Cornelius Vanderbilt Public School 14 Staten Island NY 1965-1971

Community:

Dorothy Ambrosino, Michael Keohane, Sandra Boyd

Joseph Palumbo

view sourceSchools:

Messmer High School Milwaukee WI 1960-1964

Community:

Maria Garcia

Joseph Palumbo

view sourceSchools:

Eli Whitney Vocational Technical School Hamden CT 1962-1966

Community:

Harold Stewart, Raymond Leete, Jean Laplante

Joseph Palumbo

view sourceSchools:

St. John De La Salle School Chicago IL 1965-1967

Community:

Sandra Hubl, Yvetta Williams, Janice Koch

Youtube

Myspace

Googleplus

Joseph Palumbo

Joseph Palumbo

Joseph Palumbo

Joseph Palumbo

Joseph Palumbo

Education:

University of Massachusetts Amherst - Communications

Joseph Palumbo

Joseph Palumbo

Joseph Palumbo

Joseph Palumbo

view source

Joseph Palumbo

view source

Dominick Joseph Palumbo

view source

Joseph Palumbo

view source

Joseph Michael Palumbo

view source

Joseph T. Palumbo

view source

Joseph Palumbo

view source

Joseph Palumbo

view sourceNews

BioVie's NE3107 Demonstrates Potential Improvements in

view source- These data suggest that NE3107 as adjunct therapy to levodopa may hold promise in ameliorating specific non-motor symptoms of Parkinsons Disease, particularly in sleep/fatigue and restlessness of the legs, stated Joseph Palumbo, BioVies Chief Medical Officer. These findings extend previously re

- Date: Mar 01, 2024

- Category: Health

- Source: Google

Plaxo

Joseph Palumbo, MBA, FCMA

view sourceToronto, Canada & Global

Joseph Palumbo

view sourceAssociate Director, CVM Marketing at Novartis Phar...

Get Report for Joseph J Palumbo from Poughkeepsie, NY, age ~63