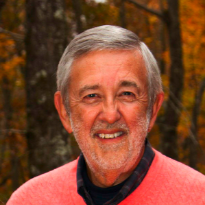

Keith Douglas Short

age ~68

from Folsom, CA

- Also known as:

-

- Keith D Short

- Keath Short

- Short Keath

Keith Short Phones & Addresses

- Folsom, CA

- Phoenix, AZ

- Cherry Hill, NJ

- 5663 109Th Ave, Westminster, CO 80020 • 3034693272

- Broomfield, CO

- Centennial, CO

- Irving, TX

- Arapahoe, CO

- Marshalltown, IA

- 5663 W 109Th Cir, Westminster, CO 80020

Work

-

Company:Cbs corporation inc2005

-

Position:Principal engineer, data networks

Education

-

School / High School:New York City Technical College1995

-

Specialities:Bachelor of Technology in Telecommunications

Wikipedia References

Keith Short

Work:

Business category:

Sculptors

Education:

Specialty:

Sculptor

Skills & Activities:

Activity:

Films

Name / Title

Company / Classification

Phones & Addresses

Architect

Kozio

Computer Software · Custom Computer Programing

Computer Software · Custom Computer Programing

2015 Ionosphere St SUITE 201, Longmont, CO 80504

1801 Sunset Pl, Longmont, CO 80501

202 Main St, Longmont, CO 80501

8665130391, 3037761356

1801 Sunset Pl, Longmont, CO 80501

202 Main St, Longmont, CO 80501

8665130391, 3037761356

SHORT FINANCIAL SOLUTIONS LLC

8125 N 23 Ave #110 H, Phoenix, AZ 85021

Resumes

Keith Short

view source

Keith Short

view source

Keith Short

view source

Keith Short Easton, PA

view sourceWork:

CBS Corporation Inc

2005 to 2000

Principal Engineer, Data Networks Viacom Inc

New York, NY

2000 to 2005

Senior Network Engineer Prudential Securities

New York, NY

1997 to 2000

Network Engineer - Implementation/ Assistant Vice President

2005 to 2000

Principal Engineer, Data Networks Viacom Inc

New York, NY

2000 to 2005

Senior Network Engineer Prudential Securities

New York, NY

1997 to 2000

Network Engineer - Implementation/ Assistant Vice President

Education:

New York City Technical College

1995 to 1997

Bachelor of Technology in Telecommunications New York City Technical College

1993 to 1995

Associates in Electrical Engineering Technology Data Center Technologies

1995 to 1997

Bachelor of Technology in Telecommunications New York City Technical College

1993 to 1995

Associates in Electrical Engineering Technology Data Center Technologies

Isbn (Books And Publications)

Software Factories: Assembling Applications with Patterns,Models, Frameworks, and Tools

view sourceAuthor

Keith Short

ISBN #

0471202843

License Records

Doctor Of Chiropractic

Address:

5020 S Federal, Broomfield, CO 80038

License #:

4331 - Expired

Issued Date:

Oct 11, 1996

Renew Date:

Jul 31, 2001

Expiration Date:

Jul 31, 2001

Type:

Chiropractic

Keith Douglas Short

Address:

5020 S Federal, Broomfield, CO 80038

License #:

2783774 - Expired

Issued Date:

Oct 11, 1996

Renew Date:

Jul 31, 2001

Expiration Date:

Jul 31, 2001

Type:

Electrotherapy Chiropractic

Us Patents

-

System, Apparatus And Method For Multi-Level Cache In A Multi-Processor/Multi-Controller Environment

view source -

US Patent:6460122, Oct 1, 2002

-

Filed:Sep 30, 1999

-

Appl. No.:09/409929

-

Inventors:Noel S. Otterness - Boulder CO

William A. Brant - Boulder CO

Keith E. Short - Lafayette CO

Joseph G. Skazinski - Bertoud CO -

Assignee:International Business Machine Corporation - Armonk NY

-

International Classification:G06F 1200

-

US Classification:711154, 711122, 711130, 711216

-

Abstract:This inventive provides a multiple level cache structure and multiple level caching method that distributes I/O processing loads including caching operations between processors to provide higher performance I/O processing, especially in a server environment. A method of achieving optimal data throughput by taking full advantage of multiple processing resources is disclosed. A method for managing the allocation of the data caches to optimize the host access time and parity generation is disclosed. A cache allocation for RAID stripes guaranteed to provide fast access times for the XOR engine by ensuring that all cache lines are allocated from the same cache level is disclosed. Allocation of cache lines for RAID levels which do not require parity generation and are allocated in such manner as to maximize utilization of the memory bandwidth is disclosed. Parity generation which is optimized for use of the processor least utilized at the time the cache lines are allocated, thereby providing for dynamic load balancing amongst the multiple processing resources, is disclosed. An inventive cache line descriptor for maintaining information about which cache data pool the cache line resides within, and an inventive cache line descriptor which includes enhancements to allow for movement of cache data from one cache level to another is disclosed.

-

Method And Apparatus For Providing A Raid Controller Having Transparent Failover And Failback

view source -

US Patent:6578158, Jun 10, 2003

-

Filed:Oct 28, 1999

-

Appl. No.:09/429523

-

Inventors:William G. Deitz - Niwot CO

Keith Short - LaFayette CO -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 1100

-

US Classification:714 11, 714 5

-

Abstract:A method and apparatus for controlling a memory system comprising a plurality of controllers connected by a fibre channel arbitrated loop to provide transparent failover and failback mechanisms for failed controllers. The controllers are adapted to transfer data between a data storage system and at least one host computer in response to instructions therefrom. In the method, a unique identifier is provided to each controller. The operation of the controllers is then monitored and, when a failed controller is detected, a failover procedure is performed on a surviving controller. The failover procedure includes disabling the failed controller and instructing the surviving controller to assume the identity of the failed controller. Thus, the surviving controller is capable of responding to instructions addressed to it and instructions addressed to the failed controller, and the failure of the failed controller is transparent to the host computer. A computer program and a computer program product for implementing the method are also provided.

-

Embedded Test I/O Engine

view source -

US Patent:7721260, May 18, 2010

-

Filed:Sep 8, 2004

-

Appl. No.:10/711287

-

Inventors:Keith Edward Short - Lafayette CO, US

Joseph G. Skazinski - Berthoud CO, US -

Assignee:Kozio, Inc. - Longmont CO

-

International Classification:G06F 9/44

-

US Classification:717124, 717125, 717126, 717127, 717128

-

Abstract:A system and method for testing input and output paths connected to an embedded processor. Specialized test software operating on the embedded processor creates one or more test workers or threads, each having a specific routine to perform, which are executed in parallel, stressing various communication paths. The results may be analyzed to help in many different ways during the life cycle of the device with the embedded controller.

-

Apparatus, System, And Method For Automated Generation Of Embedded Systems Software

view source -

US Patent:20050120340, Jun 2, 2005

-

Filed:Sep 9, 2004

-

Appl. No.:10/937117

-

Inventors:Joseph Skazinski - Berthoud CO, US

Keith Short - LaFayette CO, US -

International Classification:G06F009/45

-

US Classification:717140000

-

Abstract:The apparatus includes an input module for receiving hardware description data. The hardware description data describes hardware components of an embedded system. The apparatus also includes a build module for generating a board support layer for interfacing with the hardware components. The system may include the apparatus, an automation server coupled to a communications network, and a graphical user interface configured to display selectable icons representative of hardware elements from a plurality of hardware element icons, organize the selected icons into a hardware design, and generate hardware description data from the hardware design. The method includes receiving hardware description data describing hardware components of an embedded system, generating an embedded system board support layer in response to the described hardware description data for interfacing with the hardware components, and compiling the embedded system board support layer into executable code.

Plaxo

Keith Short

view sourceOwner at Short Inspection Services

Flickr

Myspace

KEIth SHort

view sourceLocality:

G-BORO/WILLIAMSTON N.C, North Carolina

Gender:

Male

Birthday:

1926

Googleplus

Keith Short

Keith Short

Keith Short

Keith Short

Keith Short

Keith Short

Keith Short

Keith Short

Classmates

Keith Short

view sourceSchools:

Francis Scott Key Middle School Silver Spring MD 1980-1982

Keith Short

view sourceSchools:

Charisma Collegiate High School Springdale Peru 1995-1998, Indian River High School Springdale Peru 1996-2000

Community:

Lee Wells, Mike Blackler, Dave Wells, Stephanie Roberts

Keith Short

view sourceSchools:

Chambersburg Area High School Chambersburg PA 1975-1979

Keith Short

view sourceSchools:

Rising Sun High School Rising Sun IN 2001-2005

Community:

Amber Craig, Christian Kline, Nada Huron, Robert Skidmore

Keith Short

view sourceSchools:

Altavista High School Altavista VA 1985-1989

Community:

Stephanie Johnson

Keith Short

view sourceSchools:

Saint Juliana School Detroit MI 1966-1974

Keith Short, Baker High S...

view source

Keith Short, Falcon High ...

view sourceYoutube

Keith Short

view source

Keith Short

view source

Keith Short

view source

Keith Short

view source

Keith Short

view source

Keith Short

view source

Keith TheDagger Short

view source

James Keith Short

view sourceGet Report for Keith Douglas Short from Folsom, CA, age ~68