Michael G Alexander

age ~49

from Austin, TX

- Also known as:

-

- Michael Guy Alexander

- Michael S Alexander

- Mike G Alexander

Michael Alexander Phones & Addresses

- Austin, TX

- 1134 Sorrento Rd, Florence, AL 35630

- Alexandria, AL

Vehicle Records

-

Michael Alexander

view source -

Address:11915 Stonehollow Dr APT 422, Austin, TX 78758

-

Phone:9153337160

-

VIN:JTDBT923271115439

-

Make:TOYOTA

-

Model:YARIS

-

Year:2007

Lawyers & Attorneys

Michael Alexander

License Records

Michael B. Alexander

License #:

CPT.003110 - Expired

Issued Date:

Apr 2, 1998

Expiration Date:

Jun 30, 2000

Type:

Certified Pharmacy Technician

Michael Joseph Alexander

License #:

35381 - Expired

Issued Date:

Mar 9, 2001

Renew Date:

Apr 1, 2011

Expiration Date:

Oct 31, 2013

Type:

Professional Engineer

Michael Warren Alexander Sr

License #:

2705105243 - Active

Category:

Contractor

Issued Date:

May 1, 2006

Expiration Date:

May 31, 2018

Type:

Class C

Michael Alexander

License #:

1098 - Expired

Category:

Nursing Home Administrator

Issued Date:

Jan 1, 1971

Michael A Alexander

License #:

2989 - Active

Category:

Tow Truck Operator (Incident Management)

Expiration Date:

Jun 10, 2017

Michael Brian Alexander Md

License #:

28608 - Active

Category:

Medicine

Issued Date:

Jun 11, 2015

Effective Date:

Jun 11, 2015

Expiration Date:

Oct 1, 2018

Type:

Physician

Michael Gene Alexander

License #:

1641 - Expired

Category:

Massage Therapy

Issued Date:

May 28, 2009

Effective Date:

Aug 28, 2009

Expiration Date:

Aug 28, 2009

Type:

Temporary Massage Therapist

Michael C Alexander

License #:

2965682 - Expired

Category:

Health Care

Issued Date:

Aug 1, 1995

Effective Date:

Dec 2, 2008

Expiration Date:

Jul 31, 2002

Type:

Registered Nurse

Wikipedia References

Michael Alexander (Academic)

Michael Alexander (Trinidadian Boxer)

Michael J. Alexander

Wikipedia

Michael Alexander

view sourceMichael Alexander or Mike Alexander may refer to: Michael Alexander (academic) (born 1970), American scholar of Jewish History; Michael Alexander (bishop) ...

Resumes

Michael Alexander Saint Pete Beach, FL

view sourceWork:

Free Energy Community

Feb 2010 to 2000

Group Moderator, Founder Erica's Commercial Cleaning Service

Largo, FL

Oct 2014 to Nov 2014

Construction Cleaner Tri-Glo

Saint Petersburg, FL

Sep 2014 to Oct 2014

Floor Tech Evenings With Rebecca

Saint Pete Beach, FL

Nov 2013 to Jul 2014

Talent Scout Johnathan's Nursery

Riverview, FL

Feb 2007 to Nov 2007

Greenhouse Technician USACARAUDIO.com

Denton, TX

1996 to 2005

Sales Manager Serious Sounds Wholesale Car Audio

Denton, TX

1994 to 2003

Owner, Sales Manager

Feb 2010 to 2000

Group Moderator, Founder Erica's Commercial Cleaning Service

Largo, FL

Oct 2014 to Nov 2014

Construction Cleaner Tri-Glo

Saint Petersburg, FL

Sep 2014 to Oct 2014

Floor Tech Evenings With Rebecca

Saint Pete Beach, FL

Nov 2013 to Jul 2014

Talent Scout Johnathan's Nursery

Riverview, FL

Feb 2007 to Nov 2007

Greenhouse Technician USACARAUDIO.com

Denton, TX

1996 to 2005

Sales Manager Serious Sounds Wholesale Car Audio

Denton, TX

1994 to 2003

Owner, Sales Manager

Education:

University of North Texas

Denton, TX

1990 to 1992

RadioFilmTV/Communications Southwest Texas State University

San Marcos, TX

1986 to 1989

None in Poli Sci/Communications

Denton, TX

1990 to 1992

RadioFilmTV/Communications Southwest Texas State University

San Marcos, TX

1986 to 1989

None in Poli Sci/Communications

Skills:

Customer Service, Sales, Management, Landscaping, Construction

Michael Alexander Round Rock, TX

view sourceWork:

Sole Proprietor/Software Developer

Jun 2009 to 2000 Half Price Books

Columbus, OH

Aug 2009 to May 2013

Book Seller Texas A&M Utilities

College Station, TX

Aug 2007 to Jul 2009

IT Student Worker Texas A&M Utilities

Aug 2008 to May 2009

Student Researcher Texas A&M Utilities

Austin, TX

May 2008 to Aug 2008

Education Policy Intern

Jun 2009 to 2000 Half Price Books

Columbus, OH

Aug 2009 to May 2013

Book Seller Texas A&M Utilities

College Station, TX

Aug 2007 to Jul 2009

IT Student Worker Texas A&M Utilities

Aug 2008 to May 2009

Student Researcher Texas A&M Utilities

Austin, TX

May 2008 to Aug 2008

Education Policy Intern

Education:

Texas A&M University

College Station, TX

May 2009

Master of Public Service and Administration in leadership University of Houston

Houston, TX

May 2005

Bachelor of Science in Economics Texas A&M University

College Station, TX

May 2001

Bachelor of Science in Political Science

College Station, TX

May 2009

Master of Public Service and Administration in leadership University of Houston

Houston, TX

May 2005

Bachelor of Science in Economics Texas A&M University

College Station, TX

May 2001

Bachelor of Science in Political Science

Michael Alexander Fort Lee, VA

view sourceWork:

U.S. Army

2010 to 2000

Developer Writer U.S. Army, Camp Casey, Korea

2009 to 2010

Section Chief U.S. Army, Redstone Arsenal

Huntsville, AL

2006 to 2009

Instructor/Writer U.S. Army

Fort Sill, OK

2003 to 2006

Drill Sergeant U.S. Army, Redstone Arsenal

Huntsville, AL

2001 to 2003

Instructor/Writer

2010 to 2000

Developer Writer U.S. Army, Camp Casey, Korea

2009 to 2010

Section Chief U.S. Army, Redstone Arsenal

Huntsville, AL

2006 to 2009

Instructor/Writer U.S. Army

Fort Sill, OK

2003 to 2006

Drill Sergeant U.S. Army, Redstone Arsenal

Huntsville, AL

2001 to 2003

Instructor/Writer

Michael Alexander St. Louis, MO

view sourceWork:

Monsanto

2007 to Present

Facility Maintenance Technical Specialist Roberts Company

2006 to 2007

Facilities Manager St. Louis County

2004 to 2006

Building System Foreman Alexander's Home Improvements

2003 to 2004

Project Manager St. Louis Community College

1998 to 2003

Stationary Engineer City of Saint Louis

1994 to 1998

Stationary Engineer Lambert Airport

2007 to Present

Facility Maintenance Technical Specialist Roberts Company

2006 to 2007

Facilities Manager St. Louis County

2004 to 2006

Building System Foreman Alexander's Home Improvements

2003 to 2004

Project Manager St. Louis Community College

1998 to 2003

Stationary Engineer City of Saint Louis

1994 to 1998

Stationary Engineer Lambert Airport

Us Patents

-

Processing Of Coherent And Incoherent Accesses At A Uniform Cache

view source -

US Patent:8117399, Feb 14, 2012

-

Filed:May 7, 2009

-

Appl. No.:12/437115

-

Inventors:David F. Greenberg - Austin TX, US

Michael C. Alexander - Austin TX, US

Kathryn C. Stacer - Round Rock TX, US -

Assignee:Freescale Semiconductor, Inc. - Austin TX

-

International Classification:G06F 12/08

-

US Classification:711141, 711125

-

Abstract:Each cacheline of a unified cache storing information is marked as incoherent if the information was acquired incoherently or marked as coherent if the information was acquired coherently. A subsequent incoherent read access to a cacheline can result in a cache hit and a return of the cached information regardless of whether the cacheline is marked as coherent or incoherent. However, a subsequent coherent read access to a cacheline marked as incoherent will be returned as a cache miss regardless of whether the cacheline includes information sought by the coherent read access. In response to a cache miss for a coherent read access, a global snoop is initiated so as to query all other target components within the same coherency domain. In contrast, a cache miss resulting from an incoherent read access is processed using a non-global snoop to a limited set of one or a few target components in the coherency domain.

-

Ensuring Validity Of The Bookmark Reference In A Collaborative Bookmarking System

view source -

US Patent:20130230248, Sep 5, 2013

-

Filed:Mar 2, 2012

-

Appl. No.:13/411243

-

Inventors:Michael G. Alexander - Austin TX, US

Paul R. Bastide - Boxford MA, US

Matthew E. Broomhall - South Burlington VT, US

Beth Anne M. Collopy - Amesbury MA, US

Robert E. Loredo - North Miami Beach FL, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 15/16

G06K 9/18 -

US Classification:382182, 709205

-

Abstract:A method, system and computer program product for ensuring that the tags accurately describe a resource referenced by a bookmark in a collaborative bookmarking system. A user bookmarking an Internet resource that is referenced by a bookmark is detected. The user provides a description of the bookmark in the form of metadata, which includes tags, to be associated with the bookmark. The Internet resource is analyzed to determine its meaning. A second user bookmarking the same Internet resource that is referenced by the bookmark is detected. The second user provides a description of the bookmark in the form of metadata, which includes tags. The Internet resource is analyzed a second time to determine its meaning If the relatedness of these meanings is beyond a threshold limit, then the original bookmark metadata is invalidated and the invalidated tags are replaced with the tags provided by the second user.

-

Method And Apparatus For Synchronizing Multiple Clocks

view source -

US Patent:57427992, Apr 21, 1998

-

Filed:Feb 18, 1997

-

Appl. No.:8/801648

-

Inventors:Michael Alexander - Austin TX

Carmine Nicoletta - Austin TX

Arthur R. Piejko - Austin TX -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G06F 112

-

US Classification:395552

-

Abstract:A method and apparatus for synchronizing multiple busses having different cycle times in a data processing system (10). The present invention synchronizes multiple clocks having different phase and frequencies without redundant use of phase lock loop units. An initial unit (7) receives an external system clock having an initial phase and frequency. An internal clock (112) is generated which is a phase and frequency adjusted derivation of the system clock. From this internal clock (112) a global clock (101) for use within the data processor (10) is generated. A second unit (9) receives the internal clock (112) and performs phase adjustment to provide a peripheral clock (114). The provision of the internal clock (112) detaches the dependency of peripheral clock (114) generation from the global clock (101), while maintaining a phase relationship with the global clock (101). In one embodiment, the present invention is implemented without the costly use of multiple phase lock loops.

-

Apparatus And Method For Simultaneous Display Of Characters Of Variable Size And Density

view source -

US Patent:44357036, Mar 6, 1984

-

Filed:Jul 6, 1981

-

Appl. No.:6/280613

-

Inventors:Glenn E. Hunt - Austin TX

Michael C. Alexander - Austin TX

Gerald L. Lozano - Austin TX

Gerald O. Manktelow - Austin TX -

Assignee:Data General Corporation - Westboro MA

-

International Classification:G09G 116

-

US Classification:340723

-

Abstract:Apparatus and method for simultaneous display of alphanumeric characters of variable character density on a raster scan CRT monitor is disclosed. Circuitry is provided to supply multiple sources of timing for terminal operations, to switch among timing sources without display degradation, and to vary the number of dots per raster line that constitute a character field. The density of displayed characters may be changed, under user control, for each character row.

-

System For Data Synchronization Between Two Devices Using Four Time Domains

view source -

US Patent:57817650, Jul 14, 1998

-

Filed:Nov 3, 1995

-

Appl. No.:8/552657

-

Inventors:Michael C. Alexander - Austin TX

-

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G06F 104

-

US Classification:395551

-

Abstract:A system for data synchronization in a bus interface unit (12) controls the flow of data between data processor (10) operating at a higher clock rate and the address and data buses operating at a lower clock rate. The data synchronization system incorporates circuit paths operating in four different clock domains: core-rate, bus-rate, transfer-rate, and receive-rate. Circuits processing data solely at the higher clock rate of the data processor or the lower clock rate of the address and data buses operate in the core-rate or bus-rate domains, respectively. The transfer-rate domain is used to transfer data from the core-rate to the bus-rate. Conversely, the receive-rate domain is used to transfer data from the bus-rate to the core-rate. The data synchronization system provides a general solution to the problem unreliable half cycle data paths.

-

Data Processor With Circuit For Regulating Instruction Throughput While Powered And Method Of Operation

view source -

US Patent:60290064, Feb 22, 2000

-

Filed:Dec 23, 1996

-

Appl. No.:8/772713

-

Inventors:Michael Alexander - Austin TX

Belliappa Kuttanna - Austin TX -

Assignee:Motorola, Inc. - Schaumburg IL

-

International Classification:G06F 132

-

US Classification:39575005

-

Abstract:A data processor (10) incorporates instruction regulating or "throttling" circuitry (31) for limiting consumed power. A user visible register maintains an INTERVAL field by which instruction fetch from an instruction cache (14) is periodically delayed. This INTERVAL field may be adjusted to suit the power budget of the data processor.

-

Circuitry And Method For Reducing Power Consumption Within An Electronic Circuit

view source -

US Patent:54208084, May 30, 1995

-

Filed:May 13, 1993

-

Appl. No.:8/061397

-

Inventors:Michael C. Alexander - Austin TX

Arturo L. Arizpe - Buda TX

Gianfranco Gerosa - Austin TX

James A. Kahle - Austin TX

Aubrey D. Ogden - Round Rock TX -

Assignee:International Business Machines Corporation - Armonk NY

Motorola, Inc. - Schaumburg IL -

International Classification:G06F 132

-

US Classification:364707

-

Abstract:A method and circuitry are provided, in which a first operation is performed with first circuitry. A second operation is performed with second circuitry. A first signal is generated in response to the first operation. A second signal is generated in response to the second operation. Power consumption is adjusted within the second circuitry in response to the first and second signals.

-

Video Terminal Character Generator

view source -

US Patent:44464576, May 1, 1984

-

Filed:Jul 6, 1981

-

Appl. No.:6/280612

-

Inventors:Michael C. Alexander - Austin TX

-

Assignee:Data General Corporation - Westboro MA

-

International Classification:G09G 116

-

US Classification:340745

-

Abstract:A raster scan CRT character generator comprising a memory having dot patterns for a plurality alphanumeric characters stored therein and a multiplexer, controlled by a signal from the memory, for selecting one of a plurality of sets of inputs to be used for determining the state of dots in the character field other than the character dot pattern.

Name / Title

Company / Classification

Phones & Addresses

Application Department

Loans

Loans

333 Westmore Dr, Toronto, ON M6H 3A6

6478865715

6478865715

Risk Management Officer

Thor Industries, Inc.

Business Services

Business Services

419 W Pike St, Leighton, AL 35646

President

Texas Network Youth Services

Professional Membership Organizations

Professional Membership Organizations

2525 Wallingwood Dr Ste 1503, Austin, TX 78746

President

Alexander Consulting Engineers, Inc

Engineering Services

Engineering Services

2525 Wallingwood Dr, Austin, TX 78746

Director

University Health Network Foundation (U.S.) Inc

President, Director

TRAILS AT CARRIAGE HILLS ASSOCIATION, INC

PO Box 203310, Austin, TX 78720

14046 Smt Dr, Austin, TX 78728

14046 Smt Dr, Austin, TX 78728

Manager

ALEXANDER NURSERIES, LLC

2813 E 22 St, Austin, TX 78722

3306 E Cesar Chavez, Austin, TX 78702

3306 E Cesar Chavez, Austin, TX 78702

Secretary, Chairman

The Reserve at Ocoee Homeowners Association, Inc

Googleplus

Michael Alexander

Work:

Susquehanna International Group - Software Developer (2007)

Goldman Sachs - Summer Analyst (2006-2006)

Ecology & Environment, Inc - Consultant (2002-2005)

Goldman Sachs - Summer Analyst (2006-2006)

Ecology & Environment, Inc - Consultant (2002-2005)

Education:

University of Pennsylvania - Master of Computer and Information Technology, University of Maryland, College Park - BA Communication

Michael Alexander

Work:

Microsoft - Intern Software Development Engineer

Education:

Queens University Belfast - Computer Science, Antrim Grammar

Relationship:

In_a_relationship

Tagline:

Drummer, Programmer, Gamer

Michael Alexander

Work:

HRMWeb - Software Developer (2009)

Education:

University of New England - Computer Science, Australian National University - Asian Studies

Tagline:

Software Engineer living in Guangzhou, China.

Michael Alexander

Work:

Leboye Design - Internship Study (2011)

Pasar Seni ITB 2010 - Visual Director (2009-2010)

Pasar Seni ITB 2010 - Visual Director (2009-2010)

Education:

Bandung Institute of Technology - Visual Communication Design

Tagline:

Visual Enthusiast & Extrasolar Musician

Michael Alexander

Lived:

Austin, TX

Work:

IBM - Software Engineer

Education:

University of Texas at Austin

Michael Alexander

Work:

Kansas City Royals - Outfield Experience Attendent (2010)

Education:

Metropolitan Community College - Fire Sciences, Truman High School

Tagline:

It ain't how hard you hit; it's about how hard you can get hit, and keep moving forward.

Michael Alexander

Education:

Pepperdine University - MBA Candidate, University of Missouri–Columbia - Finance, Economics

Tagline:

Trading my cubicle for a surfboard!

Michael Alexander

Education:

Miami Dade College - Art and Art Education, Southwest Miami High School

Tagline:

Have you been raped by a Unicorn? That's how I learned of Magic.

Bragging Rights:

Won the Highly competitive Miami Dade Arts Scholarship twice in a row

Plaxo

Michael Alexander

view sourceStrawberry, Arizona, USA

michael alexander

view sourceRetired Sold autos for 38 years retired two years ago. Still dabble a little in sales to my friends and past customers. My email is [email protected].

Michael Alexander

view sourceVoyager Program Manager at L3 Communications

Michael Alexander

view sourceManager of Business Development at Suddenlink Medi...

Michael Alexander

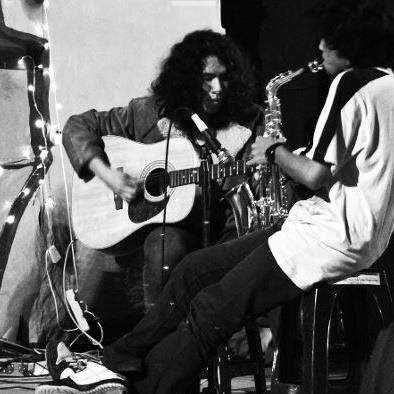

view sourceMusician at SAND

Michael Alexander

view source

Michael Alexander Taylor

view source

William Michael Alexander

view source

Michael Alexander Neumann

view source

Michael Alexander

view source

Michael Alexander

view source

Michael Alexander Scott

view source

John Michael Alexander

view sourceYoutube

Get Report for Michael G Alexander from Austin, TX, age ~49