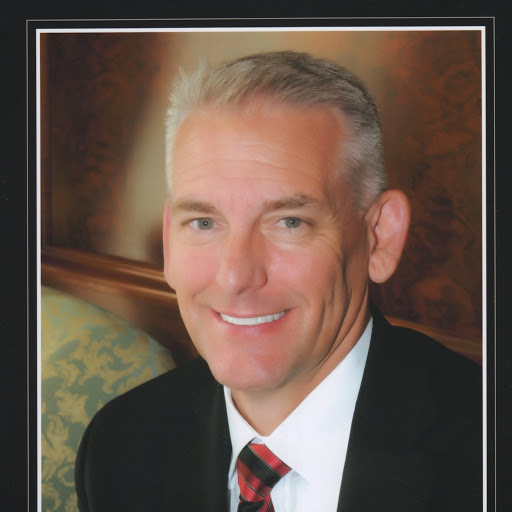

Michael Wade Choate

age ~41

from Austin, TX

- Also known as:

-

- Michael W Choate

- Mike W Choate

- Dorothy A Lawless

- Phone and address:

-

3500 Denwood Dr, Austin, TX 78759

3253158644

Michael Choate Phones & Addresses

- 3500 Denwood Dr, Austin, TX 78759 • 3253158644

- Houston, TX

- Lubbock, TX

- 1502 Paseo De Vaca St, San Angelo, TX 76901 • 3256587497

Work

-

Company:McElroy, Sullivan, Miller, Weber, and Olmstead, LLP

-

Address:1201 Spyglass Dr Ste 200, Austin, TX 78746

-

Specialities:Environmental / Natural Resources - 100%

Education

-

School / High School:Texas Tech University

Ranks

-

Licence:Texas - Eligible To Practice In Texas

-

Date:2011

Lawyers & Attorneys

Michael Wade Choate, Austin TX - Lawyer

view sourceAddress:

McElroy, Sullivan, Miller, Weber, and Olmstead, LLP

1201 Spyglass Dr Ste 200, Austin, TX 78746

5123278111 (Office), 5123276566 (Fax)

1201 Spyglass Dr Ste 200, Austin, TX 78746

5123278111 (Office), 5123276566 (Fax)

Licenses:

Texas - Eligible To Practice In Texas 2011

Education:

Texas Tech University

Specialties:

Environmental / Natural Resources - 100%

Resumes

Smts Software Test/Validation Engineer At Advanced Micro Devices

view sourceLocation:

Austin, Texas Area

Industry:

Semiconductors

Michael W Choate

view sourceLocation:

3500 Denwood Dr, Austin, TX 78759

Industry:

Non-Profit Organization Management

Work:

National Wildlife Federation Nov 2019 - May 2020

Director of Texas Water Programs

Speer South-Central Partnership For Energy Efficiency As A Resource Jan 2019 - Oct 2019

Policy Manager

Mcelroy, Sullivan & Miller Nov 2012 - Dec 2018

Associate Attorney at Mcelroy, Sullivan, Miller, Weber, and Olmstead, L.l.p

Hill+Knowlton Strategies Sep 1, 2012 - Nov 1, 2012

Fellow

Law Offices of Lynn Sherman Jan 1, 2012 - Jun 1, 2012

Attorney

Director of Texas Water Programs

Speer South-Central Partnership For Energy Efficiency As A Resource Jan 2019 - Oct 2019

Policy Manager

Mcelroy, Sullivan & Miller Nov 2012 - Dec 2018

Associate Attorney at Mcelroy, Sullivan, Miller, Weber, and Olmstead, L.l.p

Hill+Knowlton Strategies Sep 1, 2012 - Nov 1, 2012

Fellow

Law Offices of Lynn Sherman Jan 1, 2012 - Jun 1, 2012

Attorney

Education:

Texas Tech School of Law 2008 - 2010

Doctor of Jurisprudence, Doctorates, Law Baylor University 2007 - 2008

The University of Texas at Austin 2002 - 2006

Bachelors, Bachelor of Arts, English, Government Baylor University

Doctor of Jurisprudence, Doctorates, Law Baylor University 2007 - 2008

The University of Texas at Austin 2002 - 2006

Bachelors, Bachelor of Arts, English, Government Baylor University

Skills:

Legislative Relations

Legal Research

Politics

Public Policy

Environmental Awareness

Government Relations

Lobbying

Community Outreach

Public Speaking

Writing

Courts

Legal Writing

Westlaw

Environmental

Commercial Litigation

Legal Research

Politics

Public Policy

Environmental Awareness

Government Relations

Lobbying

Community Outreach

Public Speaking

Writing

Courts

Legal Writing

Westlaw

Environmental

Commercial Litigation

Languages:

Spanish

Mts, Design Engineer

view sourceLocation:

111 Finch Ln, Georgetown, TX 78626

Industry:

Semiconductors

Work:

Advanced Micro Devices since Jan 2010

SMTS System Test/Validation Engineer

Volt Technical Resources Jun 2009 - Dec 2009

Sr. Software Test Eng, contractor

Mike Choate CPU Whisperer Solutions May 2009 - Jun 2009

Owner, Principal Consultant

Volt Technical Resources Nov 2006 - Nov 2008

Strategic Technical Advisor, contractor

Mike Choate Golf Improvement School Apr 2003 - Jan 2008

Owner

SMTS System Test/Validation Engineer

Volt Technical Resources Jun 2009 - Dec 2009

Sr. Software Test Eng, contractor

Mike Choate CPU Whisperer Solutions May 2009 - Jun 2009

Owner, Principal Consultant

Volt Technical Resources Nov 2006 - Nov 2008

Strategic Technical Advisor, contractor

Mike Choate Golf Improvement School Apr 2003 - Jan 2008

Owner

Education:

Texas A&M University

Skills:

Debugging

Semiconductors

Testing

Hardware

Cross Functional Team Leadership

Microprocessors

Perl

Product Development

Product Management

Team Leadership

Processors

Electronics

Process Improvement

Engineering

Device Drivers

Soc

Hardware Architecture

Analog

Contract Negotiation

Asic

X86

Coaching

Staff Development

Recruiting

Embedded Systems

Accounting

Engineering Management

Manufacturing

Firmware

Leadership

Golf Instruction

Classroom

Ic

Strategy

Test Engineering

Functional Verification

Pcie

Process Engineering

System Testing

Team Management

Application Specific Integrated Circuits

Semiconductors

Testing

Hardware

Cross Functional Team Leadership

Microprocessors

Perl

Product Development

Product Management

Team Leadership

Processors

Electronics

Process Improvement

Engineering

Device Drivers

Soc

Hardware Architecture

Analog

Contract Negotiation

Asic

X86

Coaching

Staff Development

Recruiting

Embedded Systems

Accounting

Engineering Management

Manufacturing

Firmware

Leadership

Golf Instruction

Classroom

Ic

Strategy

Test Engineering

Functional Verification

Pcie

Process Engineering

System Testing

Team Management

Application Specific Integrated Circuits

Interests:

Social Services

Children

Economic Empowerment

Civil Rights and Social Action

Education

Environment

Science and Technology

Disaster and Humanitarian Relief

Human Rights

Animal Welfare

Arts and Culture

Health

Children

Economic Empowerment

Civil Rights and Social Action

Education

Environment

Science and Technology

Disaster and Humanitarian Relief

Human Rights

Animal Welfare

Arts and Culture

Health

Michael Choate

view source

Michael Choate

view source

Michael A Choate

view sourceIndustry:

Design

Skills:

User Experience

Responsive Web Design

Adobe Creative Suite

Visual Design

Storytelling

Sketch App

Html5

Cascading Style Sheets

Bootstrap

Web Design

Graphic Design

Interaction Design

E Commerce

Adobe Photoshop

Adobe Illustrator

Indesign

Microsoft Office

User Interface Design

User Centered Design

User Research

User Scenarios

User Stories

Facebook Marketing

Web Interface Design

Mobile Interface Design

Design Thinking

Storyboarding

Competitive Analysis

User Flows

Wireframing

User Interface Prototyping

Logo Design

Small Business

Gestalt

Cognitive Psychology

Creative Writing

Content Marketing

Social Media Marketing

Graphics

Art Direction

Social Media

Html

Html Emails

User Experience Design

Usability

Responsive Web Design

Adobe Creative Suite

Visual Design

Storytelling

Sketch App

Html5

Cascading Style Sheets

Bootstrap

Web Design

Graphic Design

Interaction Design

E Commerce

Adobe Photoshop

Adobe Illustrator

Indesign

Microsoft Office

User Interface Design

User Centered Design

User Research

User Scenarios

User Stories

Facebook Marketing

Web Interface Design

Mobile Interface Design

Design Thinking

Storyboarding

Competitive Analysis

User Flows

Wireframing

User Interface Prototyping

Logo Design

Small Business

Gestalt

Cognitive Psychology

Creative Writing

Content Marketing

Social Media Marketing

Graphics

Art Direction

Social Media

Html

Html Emails

User Experience Design

Usability

Michael Choate

view source

Michael Choate Austin, TX

view sourceWork:

AMD, INC

Jan 2010 to 2000

Senior MTS System Test/Validation Engineer Volt Technical Services

Austin, TX

Aug 2006 to Dec 2009

Sr. Software Test Engineer, AMD contractor Mike Choate Golf School

Round Rock, TX

2001 to 2007

Part-time Sole Proprietor Advanced Micro Devices, Inc

Austin, TX

1994 to 2006

MTS, Engineer > Supervisor IBM PC Company

Austin, TX

1993 to 1994

2 -shift 6-mo Contract Technician Mike Choate Gadget Repair & Design

Round Rock, TX

1992 to 1994

Sole-proprietor

Jan 2010 to 2000

Senior MTS System Test/Validation Engineer Volt Technical Services

Austin, TX

Aug 2006 to Dec 2009

Sr. Software Test Engineer, AMD contractor Mike Choate Golf School

Round Rock, TX

2001 to 2007

Part-time Sole Proprietor Advanced Micro Devices, Inc

Austin, TX

1994 to 2006

MTS, Engineer > Supervisor IBM PC Company

Austin, TX

1993 to 1994

2 -shift 6-mo Contract Technician Mike Choate Gadget Repair & Design

Round Rock, TX

1992 to 1994

Sole-proprietor

Education:

St Edwards Univ. New College

Austin, TX

Feb 1995 to Jan 2006

P.E. in FINANCE/EET Texas A&M

Bryan, TX

Bachelor of Liberal in Finance/EET

Austin, TX

Feb 1995 to Jan 2006

P.E. in FINANCE/EET Texas A&M

Bryan, TX

Bachelor of Liberal in Finance/EET

Name / Title

Company / Classification

Phones & Addresses

President

Michael R. Choate & Company, Inc.

Accountants - Certified Public

Accountants - Certified Public

2915 South Sherwood Forest Boulevard, Suite B, Baton Rouge, LA 70816-2217

2252927434, 2252933651

2252927434, 2252933651

Director, Managing

FAIRVIEW INVESTMENTS LLC

Investor

Investor

15450 Fm 1325 APT 2325, Austin, TX 78728

1021 Main St, Houston, TX 77002

16055 SPACE CENTER BLVD, Houston, TX 77062

3625 Duval Rd #116, Austin, TX 78759

1021 Main St, Houston, TX 77002

16055 SPACE CENTER BLVD, Houston, TX 77062

3625 Duval Rd #116, Austin, TX 78759

Manager

CHOATE INDUSTRIES LLC

9900 Spectrum Dr, Austin, TX 78717

MICHAEL'S BLACKTOP SEALING & REPAIR LLC

Us Patents

-

Synthesizing The Instruction Stream Executed By A Microprocessor From Its Branch Trace Data

view source -

US Patent:6658557, Dec 2, 2003

-

Filed:May 25, 2000

-

Appl. No.:09/578953

-

Inventors:Jody A. McCoy - Austin TX

Michael L. Choate - Round Rock TX -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 954

-

US Classification:712227, 712226, 714 15, 714 38, 714 39, 714 45

-

Abstract:A system for capturing the data necessary for synthesizing an instruction stream for a microprocessor. An embodiment uses a microprocessor that is adapted to write its branch trace data to the main memory. This branch trace data includes whether the microprocessor took each conditional jump encountered during the execution of a program as well as the target location of each indirect jump. The preferred embodiment further includes a logic analyzer coupled to the primary expansion bus of the target computer system. The logic analyzer captures input/output reads and writes as well as DMA transactions to the main memory. Finally, a synthesis control card controls starting a data capture as well as facilitating the transfer of information from buffers in the main memory to the control computer system. Using this information, a user may reconstruct the instruction steam as actually executed during a particular run of a program which may aide the user in performance analysis and design improvements for microprocessors.

-

System And Method For Controlling Synchronous Functional Microprocessor Redundancy During Test And Method For Determining Results

view source -

US Patent:7673188, Mar 2, 2010

-

Filed:Aug 9, 2007

-

Appl. No.:11/836201

-

Inventors:Michael L. Choate - Round Rock TX, US

Arthur M. Ryan - Round Rock TX, US

Kevin E. Ayers - Round Rock TX, US

Ha Nguyen - Round Rock TX, US

Douglas L. Terrell - Pflugerville TX, US -

Assignee:GlobalFoundries Inc. - Grand Cayman

-

International Classification:G06F 11/00

-

US Classification:714 45, 714 11

-

Abstract:A system for testing a processor. The system includes a gold processor and a test access port (TAP). A processor that is a device under test (DUT) is coupled to both the gold processor and the TAP. In the first mode, the TAP provides test signals to both the gold processor and the DUT while they operate in synchronous functional lockstep. In the second mode, the TAP provides signals to the gold processor. In the third mode, the TAP provides test signals to the DUT. A host computer coupled to the interface control unit executes a software application to cause the TAP to drive test signals and to access test output data from the gold processor and the DUT. Test output data accessed from the gold processor may be compared to that accessed from the DUT to determine any differences. The comparison data generated may then be used for further analysis.

-

System And Method For Controlling Synchronous Functional Microprocessor Redundancy During Test And Analysis

view source -

US Patent:7873874, Jan 18, 2011

-

Filed:Aug 9, 2007

-

Appl. No.:11/836200

-

Inventors:Michael L. Choate - Round Rock TX, US

Arthur M Ryan - Round Rock TX, US

Kevin E. Ayers - Round Rock TX, US

Douglas L. Terrell - Pflugerville TX, US -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 11/00

-

US Classification:714 45

-

Abstract:A system for testing a processor. The system includes a gold processor and a test access port (TAP). A processor that is a under test (DUT) is coupled to both the gold processor and the TAP. Test signals are simultaneously provided to both the gold processor and the DUT such that the gold processor and the DUT operate in synchronous functional lockstep. The TAP may also input test signals into the gold processor and DUT simultaneously and access data from each of these processors through separate test data out (TDO) connections. Test output data accessed from the gold processor may be compared to test output data accessed from the DUT to determine if any differences are present. The comparison data generated may then be used for analysis purposes.

-

Processor Test System Utilizing Functional Redundancy

view source -

US Patent:7890831, Feb 15, 2011

-

Filed:Jun 10, 2008

-

Appl. No.:12/136458

-

Inventors:Michael L. Choate - Round Rock TX, US

Mark D. Nicol - Austin TX, US

Heather L. Hanson - Austin TX, US

Michael J. Borsch - Austin TX, US

Arthur M. Ryan - Round Rock TX, US

Chandrakant Pandya - Pflugerville TX, US -

Assignee:GLOBALFOUNDRIES Inc. - Grand Cayman

-

International Classification:G06F 11/00

G01R 31/28 -

US Classification:714742, 714 10, 714 47, 714736

-

Abstract:A system and method for testing a processor. The system includes a gold processor and a test processor, wherein the test processor is the device under test (DUT). The test processor and the gold processor are identical. A first memory is coupled to the gold processor by a first memory bus and a second memory, independent of the first, is coupled to the test processor by a second memory bus. The first and second memories are identical. A memory bus comparator coupled to the first and second memory buses compares memory bus signals generated by the gold and test processors, and selectively provide a first indication if a mismatch occurs. A peripheral bus comparator is also coupled to the gold and test processors, and compares downstream transactions generated by the gold and test processors and to provide a second indication if a peripheral bus comparison results in a mismatch.

-

System And Method For Functionally Redundant Computing System Having A Configurable Delay Between Logically Synchronized Processors

view source -

US Patent:20090177866, Jul 9, 2009

-

Filed:Jan 8, 2008

-

Appl. No.:11/970793

-

Inventors:Michael L. Choate - Round Rock TX, US

Mark D. Nicol - Austin TX, US

Michael T. Clark - Austin TX, US

Scott A. White - Austin TX, US

Gregory A. Lewis - Austin TX, US

Todd Foster - Austin TX, US -

International Classification:G06F 9/30

-

US Classification:712200

-

Abstract:A method of operating a computer system. A first processor sends a first unit of binary information to an input/output (I/O) unit. The I/O unit then conveys the first unit of binary information to a functional unit in the computer system. A system response from the functional unit is then received by the I/O unit, which forwards the system response to the first processor. The system response is also stored in a first buffer. After a predetermined delay time has elapsed, the system response is then forwarded to the second processor.

-

Method And Apparatus For Optimization Of Data Writes

view source -

US Patent:58359729, Nov 10, 1998

-

Filed:May 28, 1996

-

Appl. No.:8/654437

-

Inventors:Michael L. Choate - Round Rock TX

-

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 1200

-

US Classification:711220

-

Abstract:An improved method for performing memory writes from a processor in a personal computer system is provided whereby single writes are combined into burst writes based on detection of suitable write operations in instruction code. In a preferred embodiment, the improved method is implemented in microcode. The method includes detecting multiple suitable write operations prior to the execution, collecting the data elements in a storage unit, and writing the data elements as burst write operations. Write operations that meet specific conditions for quantity of data elements to be written and specific conditions for destination address are suitable for bursting. The improved method can be implemented in existing personal computers, thereby improving system performance without requiring new software applications or a new computer board design.

License Records

Michael Joseph Choate

License #:

E-6056 - Expired

Category:

Engineering Intern

Googleplus

Michael Choate

Education:

Skiatook High School

Michael Choate

Michael Choate

Michael Choate

Michael Choate

Michael Choate

Education:

Univeristy of Texas at Austin - Government/English, Texas Tech School of Law - Environmental Law

Tagline:

Forward thinking individual, fluent in leaglese and beer.

Michael Choate

Michael Choate

Youtube

Classmates

Michael Choate

view sourceSchools:

Texas City High School Texas City TX 1984-1988

Michael Choate

view sourceSchools:

Monroe Middle School Inglewood CA 1966-1970

Community:

Diane Cornell, Luwana Huckleby, Andra Edwards

Michael Choate

view sourceSchools:

Northeast Middle School Bristol CT 1970-1978

Community:

Georgine Wood, Pearl Rhault, Robert Campbell

Michael Choate

view sourceSchools:

Alva High School Alva OK 1972-1976

Community:

Brenda Warfield, Donna Scates, Sharron Baker, Tim Brandt, Kathy Brown, Jamie Dickey, Sally Hayes, Rick Cunningham, Nieta Lohmann, Resa Harris

Michael Choate

view sourceSchools:

Lincoln East High School Lincoln NE 2009-2011

Algonquin Regional High S...

view sourceGraduates:

Sheila Ellsworth (1966-1970),

Kerry Rouhan (1985-1989),

Linda Allen (1981-1985),

Michael Choate (1967-1971),

Leonardo Meireles (2004-2008)

Kerry Rouhan (1985-1989),

Linda Allen (1981-1985),

Michael Choate (1967-1971),

Leonardo Meireles (2004-2008)

Northeast Middle School, ...

view sourceGraduates:

Michael Choate (1970-1978),

Holly Kenney (1991-1997),

Allison Rider (1993-1996),

Steven Theriault (1982-1984)

Holly Kenney (1991-1997),

Allison Rider (1993-1996),

Steven Theriault (1982-1984)

Mesquite High School, Mes...

view sourceGraduates:

Mike Stringer (1974-1978),

Charles Langley (1986-1990),

Michael Choate (1971-1975),

Julianna McEntire (1987-1991)

Charles Langley (1986-1990),

Michael Choate (1971-1975),

Julianna McEntire (1987-1991)

Michael Choate

view source

Michael Choate

view source

Michael Choate

view source

Michael Choate

view source

Michael Choate

view source

Michael Choate

view source

Sean Michael Choate

view source

Jathan Michael Choate

view sourceFlickr

Myspace

Get Report for Michael Wade Choate from Austin, TX, age ~41