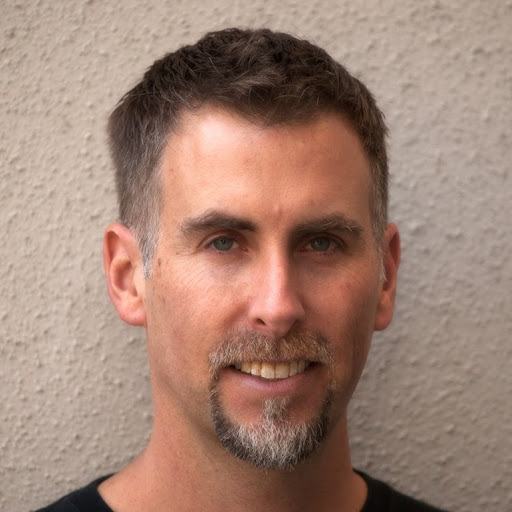

Michael Sheldon Jensen

age ~61

from Boise, ID

- Also known as:

-

- Michael S Jensen

- Mike S Jensen

- Micheal Jensen

- Michele Stoll

- Phone and address:

-

8554 W Dulcimer St, Boise, ID 83709

2086319174

Michael Jensen Phones & Addresses

- 8554 W Dulcimer St, Boise, ID 83709 • 2086319174

- Post Falls, ID

- San Jose, CA

- Sparks, NV

- Reno, NV

Medicine Doctors

Michael L. Jensen

view sourceSpecialties:

Physical Medicine & Rehabilitation

Work:

Mountain View Rehabilitation Medical Associates

380 Sierra College Dr STE 200, Grass Valley, CA 95945

5304770893 (phone), 5304771450 (fax)

380 Sierra College Dr STE 200, Grass Valley, CA 95945

5304770893 (phone), 5304771450 (fax)

Education:

Medical School

Michigan State University College of Osteopathic Medicine

Graduated: 1993

Michigan State University College of Osteopathic Medicine

Graduated: 1993

Procedures:

Neurological Testing

Osteopathic Manipulative Treatment

Physical Therapy

Physical Therapy Evaluation

Osteopathic Manipulative Treatment

Physical Therapy

Physical Therapy Evaluation

Languages:

English

Description:

Dr. Jensen graduated from the Michigan State University College of Osteopathic Medicine in 1993. He works in Grass Valley, CA and specializes in Physical Medicine & Rehabilitation. Dr. Jensen is affiliated with Dignity Health Sierra Nevada Memorial Hospital.

Michael D. Jensen

view sourceSpecialties:

Endocrinology, Diabetes & Metabolism

Work:

Mayo ClinicMayo Clinic Rochester Gonda

200 1 St SW, Rochester, MN 55905

5072842511 (phone), 5072841803 (fax)

200 1 St SW, Rochester, MN 55905

5072842511 (phone), 5072841803 (fax)

Education:

Medical School

University of Missouri, Kansas City School of Medicine

Graduated: 1979

University of Missouri, Kansas City School of Medicine

Graduated: 1979

Conditions:

Acute Renal Failure

Chronic Renal Disease

Intestinal Obstruction

Septicemia

Acute Pancreatitis

Chronic Renal Disease

Intestinal Obstruction

Septicemia

Acute Pancreatitis

Languages:

English

Description:

Dr. Jensen graduated from the University of Missouri, Kansas City School of Medicine in 1979. He works in Rochester, MN and specializes in Endocrinology, Diabetes & Metabolism. Dr. Jensen is affiliated with Mayo Clinic Hospital-Rochester Methodist Campus and Saint Marys Hospital.

Michael K. Jensen

view sourceSpecialties:

Pediatric Gastroenterology

Work:

Primary Childrens Hospital

81 N Mario Capecchi Dr FL 2, Salt Lake City, UT 84113

8016622900 (phone), 8015877539 (fax)

81 N Mario Capecchi Dr FL 2, Salt Lake City, UT 84113

8016622900 (phone), 8015877539 (fax)

Education:

Medical School

University of Utah School of Medicine

Graduated: 2004

University of Utah School of Medicine

Graduated: 2004

Languages:

English

Spanish

Spanish

Description:

Dr. Jensen graduated from the University of Utah School of Medicine in 2004. He works in Salt Lake City, UT and specializes in Pediatric Gastroenterology. Dr. Jensen is affiliated with Primary Childrens Hospital and University Of Utah Hospital.

Michael Claus Vogel Jensen

view sourceSpecialties:

Pediatrics

Pediatric Hematology-Oncology

Medical Oncology

Pediatric Hematology-Oncology

Medical Oncology

Education:

University of Pennsylvania(1990)

Michael Henrie Jensen

view sourceSpecialties:

Family Medicine

General Practice

Internal Medicine

Geriatric Medicine

General Practice

Internal Medicine

Geriatric Medicine

Education:

University of Utah (1987)

Name / Title

Company / Classification

Phones & Addresses

Fairview Capital Mortgage Broker

Mortgages

Mortgages

1708 6th Ave W, Vancouver, BC V6J5E8

CEO

Milia Construction, Inc

Concrete Contractors

Concrete Contractors

11770 Haynes Bridge Road, Suite 205-503, Alpharetta, GA 30004

7708235575

7708235575

Vice President

A & M Telecommunications

Telephone Communications. Telephone & Television Cable Contractors. Contractor - Low Voltage Systems

Telephone Communications. Telephone & Television Cable Contractors. Contractor - Low Voltage Systems

14715 Catalina St, San Leandro, CA 94577

5106780180, 5108951721

5106780180, 5108951721

Section 8 Housing Vouchers

Coupon Services

Coupon Services

369 916 W Broadway, Vancouver, BC V5Z 1K7

Vice President

A & M Telecommunications

Telephone Communications · Telephone & Television Cable Contractors · Contractor - Low Voltage Systems

Telephone Communications · Telephone & Television Cable Contractors · Contractor - Low Voltage Systems

14715 Catalina St, San Leandro, CA 94577

5106780180, 5108951721

5106780180, 5108951721

COUNTRY LIV'N HOMES, LTD

Section 8 Housing Vouchers

Coupon Services

Coupon Services

Fairview Capital Mortgage Broker

Mortgages

Mortgages

Resumes

Michael Jensen Meridian, ID

view sourceWork:

Advanced Heating and Cooling

Apr 2005 to Mar 2007

Installer CitiGroup

Sep 2001 to May 2006

Customer Service Representative Transamerica Real Estate Tax Service

Nov 1997 to Apr 2001

Tax Processor

Apr 2005 to Mar 2007

Installer CitiGroup

Sep 2001 to May 2006

Customer Service Representative Transamerica Real Estate Tax Service

Nov 1997 to Apr 2001

Tax Processor

Education:

Milan Institute

Nampa, ID

Oct 2009

Certificate in Pharmacy Technician Boise State University

General Education

Nampa, ID

Oct 2009

Certificate in Pharmacy Technician Boise State University

General Education

Michael Jensen Meridian, ID

view sourceWork:

Advanced Heating and Cooling

Apr 2005 to Mar 2007

Installer CitiGroup

Sep 2001 to May 2006

Customer Service Representative Transamerica Real Estate Tax Service

Nov 1997 to Apr 2001

Tax Processor

Apr 2005 to Mar 2007

Installer CitiGroup

Sep 2001 to May 2006

Customer Service Representative Transamerica Real Estate Tax Service

Nov 1997 to Apr 2001

Tax Processor

Education:

Milan Institute

Nampa, ID

Oct 2009

Certificate in Pharmacy Technician Boise State University

Boise, ID

2002

General Education

Nampa, ID

Oct 2009

Certificate in Pharmacy Technician Boise State University

Boise, ID

2002

General Education

Us Patents

-

Three-Tiered Translation Lookaside Buffer Hierarchy In A Multithreading Microprocessor

view source -

US Patent:7558939, Jul 7, 2009

-

Filed:Mar 8, 2005

-

Appl. No.:11/075041

-

Inventors:Soumya Banerjee - San Jose CA, US

Michael Gottlieb Jensen - Sunnyvale CA, US

Ryan C. Kinter - Sammamish WA, US -

Assignee:MIPS Technologies, Inc. - Sunnyvale CA

-

International Classification:G06F 12/00

-

US Classification:711205, 711206, 711207

-

Abstract:A three-tiered TLB architecture in a multithreading processor that concurrently executes multiple instruction threads is provided. A macro-TLB caches address translation information for memory pages for all the threads. A micro-TLB caches the translation information for a subset of the memory pages cached in the macro-TLB. A respective nano-TLB for each of the threads caches translation information only for the respective thread. The nano-TLBs also include replacement information to indicate which entries in the nano-TLB/micro-TLB hold recently used translation information for the respective thread. Based on the replacement information, recently used information is copied to the nano-TLB if evicted from the micro-TLB.

-

Instruction Encoding For System Register Bit Set And Clear

view source -

US Patent:7600100, Oct 6, 2009

-

Filed:Dec 6, 2006

-

Appl. No.:11/567290

-

Inventors:Michael Gottlieb Jensen - Sunnyvale CA, US

-

Assignee:MIPS Technologies, Inc. - Sunnyvale CA

-

International Classification:G06F 9/00

G06F 13/24 -

US Classification:712224, 712244, 710262

-

Abstract:An instruction encoding architecture is provided for a microprocessor to allow atomic modification of privileged architecture registers. The instructions include an opcode that designates the instructions are to be executed in privileged (kernel) state only, and are to communicate with privileged control registers. The instructions designate which of a plurality of privileged architecture registers is to be modified, which bit fields within the designated privileged architecture register is to be modified, and whether the designated bit fields are to be set or cleared. An instruction atomically sets or clears bit fields within privileged architecture registers, without reading the privileged architecture registers into a general purpose register. In addition, the instruction encoding allows a programmer to specify whether the previous content of a privileged architecture register is to be saved to a general purpose register during the atomic modification.

-

Instruction Encoding For System Register Bit Set And Clear

view source -

US Patent:7634638, Dec 15, 2009

-

Filed:Oct 22, 2002

-

Appl. No.:10/279210

-

Inventors:Michael Gottlieb Jensen - Sunnyvale CA, US

-

Assignee:MIPS Technologies, Inc. - Sunnyvale CA

-

International Classification:G06F 9/00

G06F 13/24 -

US Classification:712224, 712244, 710262

-

Abstract:An instruction encoding architecture is provided for a microprocessor to allow atomic modification of privileged architecture registers. The instructions include an opcode that designates to the microprocessor that the instructions are to execute in privileged (kernel) state only, and that the instructions are to communicate with privileged control registers, a field for designating which of a plurality of privileged architecture registers is to be modified, a field for designating which bit fields within the designated privileged architecture register is to be modified, and a field to designate whether the designated bit fields are to be set or cleared. The instruction encoding allows a single instruction to atomically set or clear bit fields within privileged architecture registers, without reading the privileged architecture registers into a general purpose register. In addition, the instruction encoding allows a programmer to specify whether the previous content of a privileged architecture register is to be saved to a general purpose register during the atomic modification.

-

Network System And Method For Automatically Transferring Data In A Plurality Of Input And Output Formats To A Computer Network

view source -

US Patent:7653701, Jan 26, 2010

-

Filed:Feb 23, 2001

-

Appl. No.:09/792371

-

Inventors:William D. Burns - Meridian ID, US

Michael W. Jensen - Caldwell ID, US

Loren R. Mart - Meridian ID, US -

Assignee:Hewlett-Packard Development Company, L.P. - Houston TX

-

International Classification:G06F 15/16

-

US Classification:709217, 709202, 709203, 709227

-

Abstract:A network device configured to be coupled to a network includes a plurality of input/output ports configured to be coupled to a plurality of input sources and receive a plurality of input data items. The network device includes an input device for entering destination information and output format information for each of the plurality of input data items. An interface bridge coupled to the plurality of input/output ports receives the plurality of input data items from the plurality of input/output ports and outputs the plurality of input data items using a single output protocol. A controller coupled to the interface bridges receives the plurality of input data items. The controller automatically converts each of the input data items to an output data item based on the entered destination and output format information, and automatically outputs the output data items to the network.

-

Multithreading Microprocessor With Optimized Thread Scheduler For Increasing Pipeline Utilization Efficiency

view source -

US Patent:7657891, Feb 2, 2010

-

Filed:Feb 4, 2005

-

Appl. No.:11/051979

-

Inventors:Michael Gottlieb Jensen - Sunnyvale CA, US

Darren M. Jones - Los Altos CA, US

Ryan C. Kinter - Sammamish WA, US

Sanjay Vishin - Sunnyvale CA, US -

Assignee:MIPS Technologies, Inc. - Sunnyvale CA

-

International Classification:G06F 9/46

G06F 9/40 -

US Classification:718102, 712216, 712219

-

Abstract:A multithreading processor for concurrently executing multiple threads is provided. The processor includes an execution pipeline and a thread scheduler that dispatches instructions of the threads to the execution pipeline. The execution pipeline detects a stalling event caused by a dispatched instruction, and flushes the execution pipeline to enable instructions of other threads to continue executing. The execution pipeline communicates to the scheduler which thread caused the stalling event, and the scheduler stops dispatching instructions for the thread until the stalling condition terminates. In one embodiment, the execution pipeline only flushes the thread including the instruction that caused the event. In one embodiment, the execution pipeline stalls rather than flushing if the thread is the only runnable thread. In one embodiment, the processor includes skid buffers to which the flushed instructions are rolled back so the instruction fetch pipeline need not be flushed, only the execution pipeline.

-

Prioritizing Thread Selection Partly Based On Stall Likelihood Providing Status Information Of Instruction Operand Register Usage At Pipeline Stages

view source -

US Patent:7664936, Feb 16, 2010

-

Filed:Feb 4, 2005

-

Appl. No.:11/051998

-

Inventors:Michael Gottlieb Jensen - Sunnyvale CA, US

Darren M. Jones - Los Altos CA, US

Ryan C. Kinter - Sammamish WA, US

Sanjay Vishin - Sunnyvale CA, US -

Assignee:MIPS Technologies, Inc. - Sunnyvale CA

-

International Classification:G06F 9/50

-

US Classification:712214, 712219, 718103

-

Abstract:An apparatus for scheduling dispatch of instructions among a plurality of threads being concurrently executed in a multithreading processor is provided. The apparatus includes an instruction decoder that generate register usage information for an instruction from each of the threads, a priority generator that generates a priority for each instruction based on the register usage information and state information of instructions currently executing in an execution pipeline, and selection logic that dispatches at least one instruction from at least one thread based on the priority of the instructions. The priority indicates the likelihood the instruction will execute in the execution pipeline without stalling. For example, an instruction may have a high priority if it has little or no register dependencies or its data is known to be available; or may have a low priority if it has strong register dependencies or is an uncacheable or synchronized storage space load instruction.

-

Three-Tiered Translation Lookaside Buffer Hierarchy In A Multithreading Microprocessor

view source -

US Patent:7925859, Apr 12, 2011

-

Filed:Jun 30, 2009

-

Appl. No.:12/495375

-

Inventors:Soumya Banerjee - San Jose CA, US

Michael Gottlieb Jensen - Sunnyvale CA, US

Ryan C. Kinter - Sammamish WA, US -

Assignee:MIPS Technologies, Inc. - Sunnyvale CA

-

International Classification:G06F 12/00

-

US Classification:711205, 711206, 711207, 711122, 711E12016, 711E12061, 711136

-

Abstract:A three-tiered TLB architecture in a multithreading processor that concurrently executes multiple instruction threads is provided. A macro-TLB caches address translation information for memory pages for all the threads. A micro-TLB caches the translation information for a subset of the memory pages cached in the macro-TLB. A respective nano-TLB for each of the threads caches translation information only for the respective thread. The nano-TLBs also include replacement information to indicate which entries in the nano-TLB/micro-TLB hold recently used translation information for the respective thread. Based on the replacement information, recently used information is copied to the nano-TLB if evicted from the micro-TLB.

-

Thread Instruction Fetch Based On Prioritized Selection From Plural Round-Robin Outputs For Different Thread States

view source -

US Patent:8078840, Dec 13, 2011

-

Filed:Dec 30, 2008

-

Appl. No.:12/346652

-

Inventors:Soumya Banerjee - San Jose CA, US

Michael Gottlieb Jensen - Sunnyvale CA, US -

Assignee:MIPS Technologies, Inc. - Sunnyvale CA

-

International Classification:G06F 9/46

-

US Classification:712205, 712 E9053

-

Abstract:A fetch director in a multithreaded microprocessor that concurrently executes instructions of N threads is disclosed. The N threads request to fetch instructions from an instruction cache. In a given selection cycle, some of the threads may not be requesting to fetch instructions. The fetch director includes a circuit for selecting one of threads in a round-robin fashion to provide its fetch address to the instruction cache. The circuit 1-bit left rotatively increments a first addend by a second addend to generate a sum that is ANDed with the inverse of the first addend to generate a 1-hot vector indicating which of the threads is selected next. The first addend is an N-bit vector where each bit is false if the corresponding thread is requesting to fetch instructions from the instruction cache. The second addend is a 1-hot vector indicating the last selected thread. In one embodiment threads with an empty instruction buffer are selected at highest priority; a last dispatched but not fetched thread at middle priority; all other threads at lowest priority.

License Records

Michael J Jensen

License #:

7495 - Expired

Issued Date:

Nov 30, 1982

Renew Date:

Jun 1, 2004

Expiration Date:

May 31, 2006

Type:

Certified Public Accountant

Michael S Jensen

License #:

E-5340 - Expired

Category:

Engineering Intern

Michael D Jensen

License #:

2267 - Expired

Category:

Asbestos

Issued Date:

Sep 22, 1988

Effective Date:

Sep 22, 1988

Expiration Date:

Jun 3, 1994

Type:

Asbestos Supervisor

Michael J Jensen

License #:

15357 - Expired

Category:

Emergency Medical Care

Issued Date:

Nov 14, 2002

Effective Date:

Feb 4, 2006

Expiration Date:

Dec 31, 2005

Type:

EMT

Michael David Jensen

License #:

58896 - Expired

Category:

Nursing Support

Issued Date:

Jun 15, 2007

Effective Date:

Jun 25, 2010

Expiration Date:

Jun 15, 2010

Type:

Medication Aide

Michael David Jensen

License #:

52059 - Expired

Category:

Nursing Support

Issued Date:

Apr 22, 2004

Effective Date:

May 2, 2007

Expiration Date:

Apr 22, 2007

Type:

Medication Aide

Michael Jensen

License #:

10377 - Expired

Category:

Nursing Support

Issued Date:

Jul 3, 1990

Effective Date:

May 28, 1998

Type:

Nurse Aide

Wikipedia References

Michael Aastrup Jensen

Work:

Position:

Mayor

Education:

He is also a Member of numerous committees, including the Danish delegation at the Parliamentary Assembly of the Council of Europe.

Lawyers & Attorneys

Michael Jensen - Lawyer

view sourceSpecialties:

Energy & Utilities

Litigation

Administrative Law

Appeals

Environmental and Natural Resources

Litigation

Administrative Law

Appeals

Environmental and Natural Resources

ISLN:

922718458

Admitted:

2006

Law School:

American University, Washington College of Law, J.D., 2005

Michael J. Jensen - Lawyer

view sourceAddress:

5124289094 (Office)

Licenses:

Texas - Eligible To Practice In Texas 1996

Education:

Texas Tech University School of Law

Degree - Doctor of Jurisprudence/Juris Doctor (J.D.)

Graduated - 1996

Degree - Doctor of Jurisprudence/Juris Doctor (J.D.)

Graduated - 1996

Specialties:

Probate - 100%

Michael Jensen - Lawyer

view sourceOffice:

Michael Paul Jensen

ISLN:

906171118

Admitted:

1977

University:

University of South Dakota, B.S.

Law School:

Drake University, J.D.

Michael Jensen - Lawyer

view sourceOffice:

Gorrissen Federspiel

Specialties:

Corporate Law

Banking and Finance

Banking and Finance

ISLN:

901431743

Admitted:

1987

University:

University of Copenhagen, 1984

Michael Jensen - Lawyer

view sourceSpecialties:

Personal Injury

General Practice

General Practice

ISLN:

1000552274

Admitted:

1991

Michael Jensen - Lawyer

view sourceSpecialties:

Administrative/Regulatory

Corporate

Government

Health

Corporate

Government

Health

ISLN:

906171156

Admitted:

1990

University:

Brigham Young University, B.A., 1987

Law School:

Brigham Young University, J.D., 1990

News

U.S. Military Service Is the Strongest Predictor of Carrying Out Extremist Violence

view source- crimes. Since 2011, that number has jumped to almost 45 per year, according to data from a new, unreleased report shared with The Intercept by Michael Jensen, the research director at the National Consortium for the Study of Terrorism and Responses to Terrorism, or START, at the University of Maryland.

- Date: Jan 02, 2025

- Category: U.S.

- Source: Google

His country trained him to fight. Then he turned against it. More like him are doing the same

view source- However, when people with military backgrounds radicalize, they tend to radicalize to the point of mass violence, said STARTs Michael Jensen, who leads the team that has spent years compiling and vetting the dataset.

- Date: Oct 17, 2024

- Category: World

- Source: Google

Investigation: Girl endured 7 years of sex abuse after Latter-day Saint clergy failed to report it

view source- leaders were accused of covering up the crimes committed by a young abuser from a prominent Latter-day Saint family even after hed been convicted on child sex abuse charges in Utah. The abuser, Michael Jensen, today is serving a 35- to 75-year prison sentence for abusing two children in West Virginia. T

- Date: Aug 04, 2022

- Category: World

- Source: Google

Seven years of sex abuse: How Latter-day Saint officials let it happen

view source- church leaders were accused of covering up the crimes committed by a young abuser from a prominent Mormon family even after hed been convicted on child sex abuse charges in Utah. The abuser, Michael Jensen, today is serving a 35- to 75-year prison sentence for abusing two children in West Virginia. T

- Date: Aug 04, 2022

- Category: World

- Source: Google

One gene links two different diseases

view source- Sea-turtle eggs that are incubated at warmer temperatures are more likely to produce female hatchlings. Michael Jensen at the National Oceanic and Atmospheric Administration in La Jolla, California, and his colleagues studied two groups of green turtles living on the Great Barrier Reef. One hatches

- Date: Jan 11, 2018

- Category: Health

- Source: Google

Climate Change Means 'Virtually No Male Turtles' Born In A Key Nesting Ground

view source- "Within a few degrees Celsius you go from 100 percent males to 100 percent females," says marine biologist Michael Jensen. "A really narrow range, that transition." The team's research was published this week in Current Biology.

- Date: Jan 10, 2018

- Category: Sci/Tech

- Source: Google

More Female Sea Turtles Born as Temperatures Rise

view source- The gender shift suggests that climate change is having a significant effect on one of the biggest green turtle populations in the world, said Michael Jensen, lead author of the new study, published in Current Biology.

- Date: Jan 10, 2018

- Category: Sci/Tech

- Source: Google

Warming ocean water is turning 99 percent of these sea turtles female

view source- The sex ratio in the overall population is nothing out of the ordinary, with roughly one juvenile male for every four juvenile females, says study coauthor Michael Jensen, a marine biologist with the National Oceanic and Atmospheric Administration in La Jolla, Calif. But breaking the data down by

- Date: Jan 08, 2018

- Category: Science

- Source: Google

Michael Jensen

view source

Michael Jensen

view source

Michael Jensen

view source

Michael Jensen

view source

Michael Jensen

view source

Michael S. Jensen

view source

Sean Michael Jensen

view source

Michael Jensen

view sourceMyspace

Plaxo

Michael Jensen

view sourceGraasten, DenmarkDirector of Purchasing at Danfoss Drives A/S

Michael Jensen

view source

Michael Jensen

view source

Michael Jensen

view sourceCEO at Henkal Ejendomme Past: Team Leader at Dansk System Industri, Team Leader at Delfin Software

Michael Jensen

view sourceKey Account Manager at Telenor - Cybercity

Michael Jensen

view sourceExport manager at F Engel Sunwill

Michael Jensen

view sourceINZPIRATOR

Michael Jensen

view sourceSuhrs

Youtube

Googleplus

Michael Jensen

Work:

National Academies - Director of Strategic Web Commuications (2007-2012)

National Academies - Director of Web Communications (2002-2007)

National Academies Press - Director of Publishing Technologies (1998-2007)

Johns Hopkins University Press - Electronic Publisher (1995-1998)

University of Nebraska Press - Electronic Media Manager (1989-1995)

National Academies - Director of Web Communications (2002-2007)

National Academies Press - Director of Publishing Technologies (1998-2007)

Johns Hopkins University Press - Electronic Publisher (1995-1998)

University of Nebraska Press - Electronic Media Manager (1989-1995)

About:

Longtime digital scholarly publisher. National Academies science communicator. Led development of Project Muse (Johns Hopkins University Press) for 2.5 years, and led online publishing program for th...

Tagline:

Liked CP/M on 8" disks. Loved Telnet. Facebook: Get off my lawn! Humans: Let's talk.

Bragging Rights:

I've been very lucky to have opportunities, from pre-Gopher to post-javascript.

Michael Jensen

Lived:

Santa Clara, CA

Santa Rosa, CA

Santa Rosa, CA

Work:

Mike's Bikes - IT Support

Education:

Santa Clara University - Computer Science

Tagline:

Just a general nerd that loves Apple and technology

Michael Jensen

Work:

Rimi - Vikar (2009)

Education:

Halden Vidregående - Byggteknikk, Halden Vidregående - Almen

Relationship:

Single

About:

Nissen veit best!

Bragging Rights:

Jensen Fra Grensen

Michael Jensen

Work:

PowderTech, LLC - Maintenance & Quality Manager (2006-2012)

United State Navy, Submarines - Electrician's Mate (1996-2006)

Emerson Electric Company - Production Line Lead (1994-1996)

JII - Machine Operator (1989-1994)

J&J Worldwide Services - Project Manager (2012)

United State Navy, Submarines - Electrician's Mate (1996-2006)

Emerson Electric Company - Production Line Lead (1994-1996)

JII - Machine Operator (1989-1994)

J&J Worldwide Services - Project Manager (2012)

Michael Jensen

Work:

Self - Consultant (1985)

Education:

University of Guelph - Resource Management, Queens University Belfast - Biology

About:

Born Durban, grew up Johannesburg, studied and worked in UK, Ireland and Canada, also spends time in Sri Lanka and Brazil.

Michael Jensen

Work:

Self Employed - IPhone Tech

Self Employed - Free-Lance Yachtsman

Self Employed - Free-Lance Yachtsman

Education:

University of Montana - Missoula

Tagline:

Lord I was born a rambling man...

Michael Jensen

Education:

Charlotteskolen - 0.-9. Grade/Class, Roskilde Tekniske Gymnasium - Mat/IT + English

About:

Fan of motorcycles and computers. Attending Roskilde Festival, and throwing Vallahby-parties from time to time.

Tagline:

Jensen - Says it all I think.

Michael Jensen

Lived:

San Jose, CA, United States

Work:

Luxology/The Foundry - Modo QA Manager (2010)

Education:

University of Colorado at Boulder

Get Report for Michael Sheldon Jensen from Boise, ID, age ~61