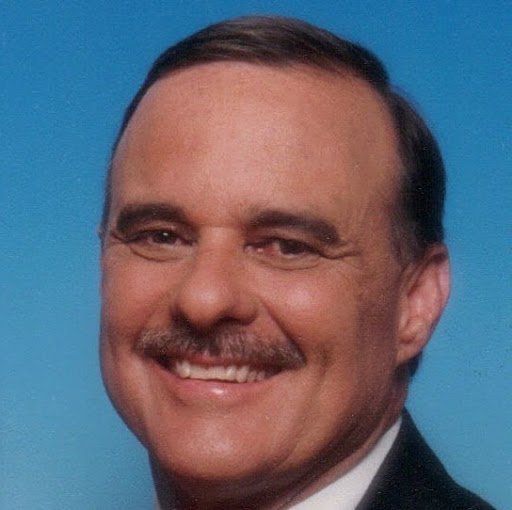

Michael Lee Mayfield

age ~58

from Weatherford, TX

- Also known as:

-

- Michael L Mayfield

- Michael I Mayfield

- Michael E Mayfield

- Mike L Mayfield

- Mike E Mayfield

- Michael Mayfield Lee

- Lee G Mayfield

- Michae Mayfield

- Michael Mayfielld

- Michael Lmayfield

- Phone and address:

- 3950 Greenwood Rd, Weatherford, TX 76088

Michael Mayfield Phones & Addresses

- 3950 Greenwood Rd, Weatherford, TX 76088

- 122 Buckingham Ct, Weatherford, TX 76088 • 8175997201

- Belton, TX

- Pflugerville, TX

- Lewisville, TX

- Blue Mound, TX

- Minden, LA

- Round Rock, TX

- Palatine, IL

Medicine Doctors

Michael E. Mayfield

view sourceSpecialties:

Psychiatry

Work:

Mayfield & Associates

670 Hillcrest Rd NW STE 300, Lilburn, GA 30047

7705640590 (phone), 7705648565 (fax)

670 Hillcrest Rd NW STE 300, Lilburn, GA 30047

7705640590 (phone), 7705648565 (fax)

Education:

Medical School

University of Tennessee College of Medicine at Memphis

Graduated: 1984

University of Tennessee College of Medicine at Memphis

Graduated: 1984

Procedures:

Psychiatric Diagnosis or Evaluation

Psychiatric Therapeutic Procedures

Psychiatric Therapeutic Procedures

Conditions:

Anxiety Dissociative and Somatoform Disorders

Anxiety Phobic Disorders

Attention Deficit Disorder (ADD)

Autism

Bipolar Disorder

Anxiety Phobic Disorders

Attention Deficit Disorder (ADD)

Autism

Bipolar Disorder

Languages:

English

Description:

Dr. Mayfield graduated from the University of Tennessee College of Medicine at Memphis in 1984. He works in Lilburn, GA and specializes in Psychiatry.

Michael B. Mayfield

view sourceSpecialties:

General Surgery

Work:

Cardiology ClinicMichael B Mayfield MD

2729 S Hwy 65 82, Lake Village, AR 71653

8702659364 (phone), 8702659366 (fax)

2729 S Hwy 65 82, Lake Village, AR 71653

8702659364 (phone), 8702659366 (fax)

Education:

Medical School

University of Arkansas College of Medicine at Little Rock

Graduated: 1992

University of Arkansas College of Medicine at Little Rock

Graduated: 1992

Languages:

English

Spanish

Spanish

Description:

Dr. Mayfield graduated from the University of Arkansas College of Medicine at Little Rock in 1992. He works in Lake Village, AR and specializes in General Surgery. Dr. Mayfield is affiliated with Chicot Memorial Medical Center.

Us Patents

-

Cache Prefetching Of L2 And L3

view source -

US Patent:6446167, Sep 3, 2002

-

Filed:Nov 8, 1999

-

Appl. No.:09/435861

-

Inventors:Michael John Mayfield - Austin TX

Francis Patrick OConnell - Austin TX

David Scott Ray - Georgetown TX -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 938

-

US Classification:711122, 711 3, 711118, 711119, 711133, 711137, 711144

-

Abstract:A data processing system includes a processor having a first level cache and a prefetch engine. Coupled to the processor are a second level cache and a third level cache and a system memory. Prefetching of cache lines is performed into each of the first, second, and third level caches by the prefetch engine. Prefetch requests from the prefetch engine to the second and third level caches is performed over a private prefetch request bus, which is separate from the bus system that transfers data from the various cache levels to the processor. The prefetch request may include a signal notifying the third level cache to also prefetch.

-

Efficient Store Machine In Cache Based Microprocessor

view source -

US Patent:6446170, Sep 3, 2002

-

Filed:Jan 19, 1999

-

Appl. No.:09/232239

-

Inventors:Kin Shing Chan - Austin TX

Dwain Alan Hicks - Pflugerville TX

Michael John Mayfield - Austin TX

Shih-Hsiung Stephen Tung - Austin TX -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 1200

-

US Classification:711132, 711133, 711210

-

Abstract:A method of retiring operations to a cache. Initially, a first operation is queued in a stack such as the store queue of a retire unit. The first operation is then copied, in a first transfer, to a latch referred to as the miss latch in response to a resource conflict that prevents the first operation from accessing the cache. The first operation is maintained in the stack for the duration of the resource conflict. When the resource conflict is resolved, the cache is accessed, in a first cache access, with the first operation from the stack. Preferably, the first operation is removed from the stack when the resource conflict is resolved and the first cache access is initiated. In the preferred embodiment, the first operation is maintained in the miss latch until the first cache access results in a cache hit. One embodiment of the invention further includes accessing the cache, in a first miss access, with the first operation from the miss latch in response to a cache miss that resulted from the first cache access. In a presently preferred embodiment, a second access is executed to access the cache with a second operation queued in the stack in response to a cache hit resulting from the first cache access.

-

System And Method For Prefetching Data To Multiple Levels Of Cache Including Selectively Using A Software Hint To Override A Hardware Prefetch Mechanism

view source -

US Patent:6460115, Oct 1, 2002

-

Filed:Nov 8, 1999

-

Appl. No.:09/435865

-

Inventors:James Allan Kahle - Austin TX

Michael John Mayfield - Austin TX

Francis Patrick OConnell - Austin TX

David Scott Ray - Georgetown TX

Edward John Silha - Austin TX

Joel Tendler - Austin TX -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 1300

-

US Classification:711122, 711137, 711213, 712207

-

Abstract:A data processing system and method for prefetching data in a multi-level code subsystem. The data processing system includes a processor having a first level cache and a prefetch engine. Coupled to the processor are a second level cache, and a third level cache and a system memory. Prefetching of cache lines is concurrently performed into each of the first, second, and third level caches by the prefetch engine. Prefetch requests from the prefetch engine to the second and third level caches are performed over a private or dedicated prefetch request bus, which is separate from the bus system that transfers data from the various cache levels to the processor. A software instruction or hint may be used to accelerate the prefetch process by overriding the normal functionality of the hardware prefetch engine.

-

System And Method For Prefetching Data Using A Hardware Prefetch Mechanism

view source -

US Patent:6535962, Mar 18, 2003

-

Filed:Nov 8, 1999

-

Appl. No.:09/435860

-

Inventors:Michael John Mayfield - Austin TX

Francis Patrick OConnell - Austin TX

David Scott Ray - Georgetown TX -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 1200

-

US Classification:711137, 711122, 711204, 712207

-

Abstract:A data processing system includes a processor having a first level cache and a prefetch engine. Coupled to the processor are a second level cache and a third level cache and a system memory. Prefetching of cache lines is performed into each of the first, second, and third level caches by the prefetch engine. Prefetch requests from the prefetch engine to the second and third level caches is performed over a private prefetch request bus, which is separate from the bus system that transfers data from the various cache levels to the processor.

-

Software Prefetch System And Method For Predetermining Amount Of Streamed Data

view source -

US Patent:6574712, Jun 3, 2003

-

Filed:Apr 14, 2000

-

Appl. No.:09/550180

-

Inventors:James Allan Kahle - Austin TX

Michael John Mayfield - Austin TX

Francis Patrick OConnell - Austin TX

David Scott Ray - Georgetown TX

Edward John Silha - Austin TX

Joel M. Tendler - Austin TX -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 1208

-

US Classification:711137, 711122, 711213, 712207

-

Abstract:A data processing system includes a processor having a first level cache and a prefetch engine. Coupled to the processor are a second level cache and a third level cache and a system memory. Prefetching of cache lines is performed into each of the first, second, and third level caches by the prefetch engine. Prefetch requests from the prefetch engine to the second and third level caches is performed over a private prefetch request bus, which is separate from the bus system that transfers data from the various cache levels to the processor. A software instruction is used to accelerate the prefetch process by overriding the normal functionality of the hardware prefetch engine. The instruction also limits the amount of data to be prefetched.

-

Programmable Data Prefetch Pacing

view source -

US Patent:6578130, Jun 10, 2003

-

Filed:Oct 18, 2001

-

Appl. No.:09/981880

-

Inventors:Brian David Barrick - Pflugerville TX

Michael John Mayfield - Austin TX

Brian Patrick Hanley - Austin TX -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 1200

-

US Classification:711213, 711137, 711204

-

Abstract:A method and apparatus for prefetching data in computer systems that tracks the number of prefetches currently active and compares that number to a preset maximum number of allowable prefetches to determine if additional prefetches should currently be performed. By limiting the number of prefetches being performed at any given time, the use of system resources for prefetching can be controlled, and thus system performance can be optimized.

-

Method And System For Implementing Remstat Protocol Under Inclusion And Non-Inclusion Of L1 Data In L2 Cache To Prevent Read-Read Deadlock

view source -

US Patent:6587930, Jul 1, 2003

-

Filed:Sep 23, 1999

-

Appl. No.:09/404400

-

Inventors:Sanjay Raghunath Deshpande - Austin TX

Peter Steven Lenk - Austin TX

Michael John Mayfield - Austin TX -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F 1200

-

US Classification:711144, 711145, 711122

-

Abstract:A distributed system structure for a large-way, multi-bus, multiprocessor system using a bus-based cache-coherence protocol is provided. The distributed system structure contains an address switch, multiple memory subsystems, and multiple master devices, either processors, I/O agents, or coherent memory adapters, organized into a set of nodes supported by a node controller. The node controller receives commands from a master device, communicates with a master device as another master device or as a slave device, and queues commands received from a master device. The system allows for the implementation of a bus protocol that reports the state of a cache line to a master device along with the first beat of data delivery for a cacheable coherent Read. Since the achievement of coherency is distributed in time and space, the issue of data integrity is addressed through a variety of actions. In one implementation, the node controller helps to maintain cache coherency for commands by blocking a master device from receiving certain transactions so as to prevent Read-Read deadlocks.

-

Method And Apparatus For Mapping Software Prefetch Instructions To Hardware Prefetch Logic

view source -

US Patent:6915415, Jul 5, 2005

-

Filed:Jan 7, 2002

-

Appl. No.:10/042102

-

Inventors:Michael John Mayfield - Austin TX, US

Francis Patrick O'Connell - Austin TX, US

David Scott Ray - Georgetown TX, US -

Assignee:International Business Machines Corporation - Armonk NY

-

International Classification:G06F009/30

-

US Classification:712225, 712205, 711137

-

Abstract:A method and apparatus for mapping some software prefetch instructions in a microprocessor system to a modified set of hardware prefetch instructions and executing the software prefetch by invoking the corresponding modified hardware prefetch instruction. For common software prefetch access patterns, by mapping the software prefetches to hardware, improved prefetching can be achieved without the need for additional hardware.

Name / Title

Company / Classification

Phones & Addresses

Superintendent

Bartlett Isd (014-902)

Elementary and Secondary Schools

Elementary and Secondary Schools

Po Box 170, Bartlett, TX 76511

Principal

Mayfield Log

Nonclassifiable Establishments

Nonclassifiable Establishments

304 S Record St, Dallas, TX 75202

Managing

Texas Espresso LLC

ENYSE MANAGEMENT LLC

MAYFIELD & SONS, LLC

MAYFIELD'S DONUTS DBA PARADISE DONUTS LLC

Owner

Michael M Mayfield

Mortgage Broker

Mortgage Broker

6218 Ledge Mtn Dr, Austin, TX 78731

5124522880

5124522880

Director

THE DEALER OF DIAMONDS INC

2050 N Stemmons Fwy UNIT 211, Dallas, TX 75207

PO Box 420727, Dallas, TX 75342

PO Box 671029, Dallas, TX 75367

PO Box 420727, Dallas, TX 75342

PO Box 671029, Dallas, TX 75367

Resumes

Michael Mayfield Alton, IL

view sourceWork:

Samsung Austin Semiconductor

Austin, TX

Feb 2011 to Jul 2013

Equipment Technician Level 2 United States Navy

Sep 2006 to Sep 2010

Interior Communications Electrician

Austin, TX

Feb 2011 to Jul 2013

Equipment Technician Level 2 United States Navy

Sep 2006 to Sep 2010

Interior Communications Electrician

Michael Mayfield Alton, IL

view sourceWork:

Samsung Austin Semiconductor

Austin, TX

Feb 2011 to Jul 2013

Equipment Technician Level United States Navy

Sep 2006 to Sep 2010

Interior Communications Electrician PO3

Austin, TX

Feb 2011 to Jul 2013

Equipment Technician Level United States Navy

Sep 2006 to Sep 2010

Interior Communications Electrician PO3

License Records

Michael L Mayfield

License #:

6446 - Active

Category:

Emergency Medical Care

Issued Date:

Dec 31, 1995

Expiration Date:

Dec 31, 2017

Type:

EMT

Michael L Mayfield

License #:

2501 - Expired

Category:

Emergency Medical Care

Issued Date:

Dec 31, 1995

Effective Date:

Mar 8, 1999

Type:

EMT A/D

Michael James Mayfield Jr

License #:

74263 - Expired

Category:

Nursing Support

Issued Date:

Jan 31, 2013

Effective Date:

Feb 10, 2015

Expiration Date:

Jan 31, 2015

Type:

Medication Aide

Michael James Mayfield Jr

License #:

62705 - Expired

Category:

Nursing Support

Issued Date:

Dec 8, 2008

Effective Date:

Dec 18, 2010

Expiration Date:

Dec 8, 2010

Type:

Medication Aide

Isbn (Books And Publications)

The Rivers of Costa Rica: A Canoeing, Kayaking, and Rafting Guide

view sourceAuthor

Michael W. Mayfield

ISBN #

0897320832

Lawyers & Attorneys

Michael Daniel Mayfield - Lawyer

view sourceAddress:

4807103117 (Office)

Licenses:

Arizona - Active 2012

Education:

Arizona State

Michael Mayfield - Lawyer

view sourceOffice:

Ray Quinney & Nebeker P.C.

Specialties:

Commercial Litigation

Bankruptcy Litigation

Motor Vehicle Dealer Law

Banking and Financial Institutions

Commercial

General Practice

Bankruptcy Litigation

Motor Vehicle Dealer Law

Banking and Financial Institutions

Commercial

General Practice

ISLN:

913170647

Admitted:

1998

University:

University of Utah, B.A., 1995

Law School:

University of Utah, J.D., 1998

Michael Mayfield - Lawyer

view sourceISLN:

905071174

Admitted:

1986

University:

University of Iowa, B.A., 1972

Law School:

Loyola University, J.D., 1986

Michael Andrew Mayfield

view source

Michael Joseph Mayfield

view source

Michael Anthony Mayfield

view source

Michael Blake Mayfield

view source

Michael Neil Mayfield

view source

Michael Heath Mayfield

view source

Michael Squishy Mayfield

view source

Michael Javon Mayfield

view sourceYoutube

Classmates

Michael Mayfield

view sourceSchools:

Nash Junior High School Smyrna GA 1960-1964

Community:

John Towery, Steve Pledger, Richard Flores

Michael Mayfield

view sourceSchools:

John F. Kennedy Middle School Suffolk VA 1978-1982

Community:

Ronald Holliman, Valerie Phillips, Archie Jackson, Karl Jones

Michael Mayfield

view sourceSchools:

Burris Laboratory School Muncie IN 1967-1971

Community:

Susie Steventon, Anthony Guarino, Jane Raisor

Michael Mayfield

view sourceSchools:

Westwind Elementary School Phoenix AZ 1977-1981

Community:

Amanda Riley, Tisha Laine, Linda Steele, Cathay Murry, Michelle Reynolds, Marylyn Bombardier

Michael Mayfield

view sourceSchools:

Bow Basin High School Medicine Bow WY 1993-1997

Community:

Jason Combe, Elayne Porterfield, Matt Newman, Todd Caldwell, Donald Wyatt

Michael Mayfield

view sourceSchools:

Boone High School Boone IA 1977-1981

Community:

Bette Hicks, Don Whitmer

Michael Mayfield

view sourceSchools:

Van Buren High School Spencer TN 1965-1969

Community:

Tamela Templeton

Michael Mayfield

view sourceSchools:

Winona High School Winona TX 1987-1991

Community:

Leland R, Patti Hawkins, Joey Green, Billy Womack

Plaxo

Michael Mayfield

view sourceLongmont, COSVP, Global Sales & Services at AEPONA

Michael Mayfield

view source63118owner at sounds terrific

Michael Mayfield

view sourceBarton Pontiac GMC

Flickr

Googleplus

Michael Mayfield

Lived:

Austin, Tx

Austin, Texas

Austin, Texas

Work:

Dream House, Realtors - Owner (1980)

About:

We are the Broker / Owner of Dream House, Realtors in Austin, Tx and have been in business since 1978.

Michael Mayfield

Work:

Wachovia education finance

Vision service plan

Vision service plan

Education:

Elko high school

Michael Mayfield

Lived:

Dallas, TX

Relationship:

Single

About:

OLD SKOOL...Hopelessly stuck in the 1980's...

Michael Mayfield

Work:

Aepona - SVP Global Customer Operations

Michael Mayfield

Michael Mayfield

Michael “Clockfuey” Mayfi...

Michael Mayfield

Get Report for Michael Lee Mayfield from Weatherford, TX, age ~58