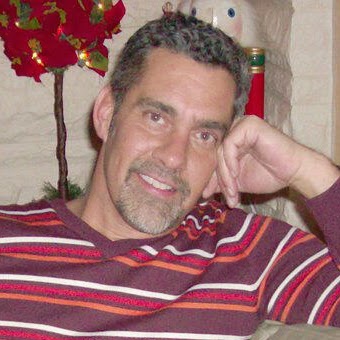

Michael W Yeager

age ~67

from Colorado Springs, CO

- Also known as:

-

- Michael William Yeager

- Michael R Yeager

- Micheal W Yeager

- Mike R Yeager

- Mike W Yeager

- Carolyn M Yeager

- Michael Yaeger

- Phone and address:

-

7330 Woodmen Mesa Cir, Colorado Springs, CO 80919

7195930520

Michael Yeager Phones & Addresses

- 7330 Woodmen Mesa Cir, Colorado Springs, CO 80919 • 7195930520

- 772 Rockrimmon Blvd, Colorado Springs, CO 80919 • 7195906269

- Colorado Spgs, CO

- Corona del Mar, CA

- Laguna Niguel, CA

- McMurray, PA

- Larkspur, CO

- Linesville, PA

- Chicago, IL

- Library, PA

- Venice, FL

- Nokomis, FL

- Clint, TX

Work

-

Company:Schoolsfirst federal credit unionOct 2005

-

Position:Network administrator i/helpdesk specialist ii

Education

-

School / High School:Park University- Parkville, MO2004

-

Specialities:Bachelor of Science in Science Management/Computer Information Systems

Languages

English

Specialities

Speech-Language Pathology

Resumes

The World Is Crazy!

view sourcePosition:

tech at self employed (Self-employed)

Location:

United States

Industry:

Automotive

Work:

self employed

tech

tech

Product Support Engineer At Aircomm International.off To The Races !!

view sourcePosition:

Product Support Engineer at Aircomm International

Location:

Bothell, Washington

Industry:

Telecommunications

Work:

Aircomm International since Jan 2013

Product Support Engineer

Alaska Communications - Anchorage, Alaska Area Dec 2011 - Jan 2013

Senior Network Planner

Carrier IQ Mar 2011 - Dec 2011

Certification Engineer (Consultant)

Kentrox May 2009 - Nov 2010

Sr. Services Application Engineer

Carrier IQ Feb 2007 - Feb 2009

Technical Project Manager

Product Support Engineer

Alaska Communications - Anchorage, Alaska Area Dec 2011 - Jan 2013

Senior Network Planner

Carrier IQ Mar 2011 - Dec 2011

Certification Engineer (Consultant)

Kentrox May 2009 - Nov 2010

Sr. Services Application Engineer

Carrier IQ Feb 2007 - Feb 2009

Technical Project Manager

Education:

Montana State University-Northern 2001 - 2004

BS, CIS

BS, CIS

Skills:

Wireless

GSM

CDMA

RF

OSS

Databases

Mobile Analytics

Open Source Software

Network Administration

WCDMA

DSL

GSM

CDMA

RF

OSS

Databases

Mobile Analytics

Open Source Software

Network Administration

WCDMA

DSL

Interests:

New technology, CDMA networks and issues.

Michael Jackie Yeager

view source

Michael Yeager

view source

Michael Yeager

view sourceSkills:

Microsoft Excel

Customer Service

Customer Service

Michael Yeager

view source

Property Manager

view sourceWork:

Property Manager

Michael Yeager

view sourceName / Title

Company / Classification

Phones & Addresses

Principal

Yeager Realty

Real Estate Agent/Manager

Real Estate Agent/Manager

12385 Serena Ct, Castle Rock, CO 80108

Principal

McMurray Garage Doors

Carpentry Contractor · Garage Doors

Carpentry Contractor · Garage Doors

111 Spg St, Canonsburg, PA 15317

4128488455

4128488455

NORTHGATE TRANSMISSIONS, LLC

MM

Oxford Learning Centers of America, LLC

Us Patents

-

System And Method For Write-Protecting Predetermined Portions Of A Memory Array

view source -

US Patent:53943678, Feb 28, 1995

-

Filed:Mar 18, 1994

-

Appl. No.:8/210699

-

Inventors:Jeffery E. Downs - Colorado Springs CO

Michael W. Yeager - Colorado Springs CO -

Assignee:Ramtron International Corporation - Colorado Springs CO

-

International Classification:G11C 700

G11C 1122 -

US Classification:365195

-

Abstract:A system and method wherein a predetermined soft fuse value may be written to a corresponding soft fuse register to control subsequent access to a number of lock bits in a non-volatile semiconductor memory array which are provided for selectively precluding writes to predetermined portions of the memory array. In a specific embodiment, the system and method may be utilized in conjunction with radio frequency ("RF") identification ("ID") transponders incorporating a non-volatile ferroelectric random access memory ("FRAM") array integrated circuit.

-

Method Of Making Integration Of High Value Capacitor With Ferroelectric Memory

view source -

US Patent:59096241, Jun 1, 1999

-

Filed:Oct 18, 1995

-

Appl. No.:8/544470

-

Inventors:Michael W. Yeager - Colorado Springs CO

Dennis R. Wilson - Black Forest CO -

Assignee:Ramtron International Corporation - Colorado Springs CO

-

International Classification:H01L 218242

-

US Classification:438396

-

Abstract:An integrated circuit capacitor and method for making the same utilizes a ferroelectric dielectric, such as lead-zirconate-titanate ("PZT"), to produce a high value peripheral capacitor for integration on a common substrate with a ferroelectric memory array also utilizing ferroelectric memory cell capacitors as non-volatile storage elements. The peripheral capacitor is linearly operated in a single direction and may be readily integrated to provide capacitance values on the order of 1-10 nF or more utilizing the same processing steps as are utilized to produce the alternately polarizable memory cell capacitors. The high value peripheral capacitor has application, for example, as a filter capacitor associated with the on-board power supply of a passive radio frequency ("RF") identification ("ID") transponder.

-

Write Protection For A Non-Volatile Memory

view source -

US Patent:59128496, Jun 15, 1999

-

Filed:Aug 28, 1998

-

Appl. No.:9/141564

-

Inventors:Yoshihiko Yasu - Tokyo, JP

Hiroyuki Sakai - Tokyo, JP

Michael W. Yeager - Colorado Springs CO

Donald J. Verhaeghe - Colorado Springs CO -

Assignee:Hitachi, Ltd. - Tokyo

Ramtron International Corporation - Colorado Springs CO -

International Classification:G11C 700

-

US Classification:365195

-

Abstract:A semiconductor memory device, divided into plural blocks, comprising: a memory array having a non-volatile memory element which makes the read cycle and the write cycle to be substantially equivalent; plural storage elements storing the information of write protection/permission corresponding to each said block respectively; and a setting circuit to set the information of write protection/permission to said plural storage elements, wherein said setting circuit sets the write-protection information to said plural storage elements at the write cycle after designated plural read cycles. Therefore, the write protection/permission can be set by the unit of block, block by block, so that the write-protected ROM and the RAM can be set freely. Furthermore, the complexity of the setting procedure of write protection/permission may prevent the accidental false setting caused by a system runaway and so forth.

-

Method And Apparatus For Detecting An Fsk Encoded Carrier Signal

view source -

US Patent:55330614, Jul 2, 1996

-

Filed:Feb 10, 1994

-

Appl. No.:8/194694

-

Inventors:Gregory M. Smith - Colorado Springs CO

Michael W. Yeager - Colorado Springs CO

J. Donald Pauley - Estes Park CO

Gary T. Carroll - Boulder CO -

Assignee:Racom Systems, Inc. - Englewood CO

-

International Classification:H03D 300

-

US Classification:375334

-

Abstract:An integrated FSK detector circuit includes a first counter that receives a carrier signal and provides a multiple-bit output for reducing the frequency of the carrier signal into a plurality of weighted sub-multiples. An oscillator enable decoder circuit provides predetermined calibrate and measure pulses in response to the first counter output. A gated oscillator receives the calibrate and measure pulses and provides a burst of oscillator pulses during these time intervals. A second counter has an input coupled to the output of the gated oscillator and an up/down control terminal coupled to the output of the first counter. The output of the second counter also provides a multiple-bit output for reducing the frequency of the gated oscillator pulses. An FSK decoder logic circuit decodes the multiple-bit output of the second counter into a single bit FSK detect signal. The FSK detector circuit also includes a reset circuit coupled to the first counter for resetting between FSK detections.

-

Single Chip Complex Floating Point Numeric Processor

view source -

US Patent:49966618, Feb 26, 1991

-

Filed:Oct 5, 1988

-

Appl. No.:7/253826

-

Inventors:Roger G. Cox - Colorado Springs CO

Michael W. Yeager - Colorado Springs CO

Lance L. Flake - Boulder CO -

Assignee:United Technologies Corporation - Hartford CT

-

International Classification:G06F 738

G06F 1540

G06F 1500 -

US Classification:364748

-

Abstract:A pipelined arithmetic processor includes a pair of multipliers in parallel feeding an ALU that, in turn, feeds a pair of parallel accumulators, the various sections being connected by controllable data paths and controlled by a set of pipelined registers feeding a series of decoders.

-

System And Method For Partitioning Pla Product Terms Into Distinct Logical Groups

view source -

US Patent:51896281, Feb 23, 1993

-

Filed:Mar 11, 1991

-

Appl. No.:7/667571

-

Inventors:Glenn A. Olsen - Colorado Springs CO

Chong-Ming Lee - Singapore, SG

Michael T. Yeager - Sunnyvale CA

Scott K. Pickett - Los Gatos CA -

Assignee:National Semiconductor Corporation - Santa Clara CA

-

International Classification:G06F 1560

H03K 19177 -

US Classification:364489

-

Abstract:A PLA programming system includes software routines for automatically partitioning a specified set of PLA product terms into independent partitions. Each PLA product term specifies values for a set of binary input signals, and values for a set of binary output signals. Some of the output signals are feedback signals also used as input signals. A partitioning merit value is generated for each feedback signal, and then one or more of the feedback signals are selected as target bits in accordance with the generated merit values. Then the specified set of PLA product terms are divided into partitions in accordance with the values of the input signals corresponding to the target bits. All of the PLA product terms in each partition of PLA product terms have identical input signal values corresponding to the target bits, and PLA product terms in different ones of the partitions have different input signal values corresponding to the target bits. When the partitioning process fails to generate partitions containing no more than a predefined number of PLA product terms, an extra feedback signal is added to the input and output signal list of every PLA product term. The extra input and output signals are assigned binary values such that the added feedback signal will be a good target bit for partitioning the PLA product terms, and then process of selecting target bits and partitioning the PLA product terms is repeated.

-

Integration Of High Value Capacitor With Ferroelectric Memory

view source -

US Patent:56082460, Mar 4, 1997

-

Filed:Sep 8, 1995

-

Appl. No.:8/525497

-

Inventors:Michael W. Yeager - Colorado Springs CO

Dennis R. Wilson - Black Forest CO -

Assignee:Ramtron International Corporation - Colorado Springs CO

-

International Classification:H01L 2994

-

US Classification:257295

-

Abstract:An integrated circuit capacitor and method for making the same utilizes a ferroelectric dielectric, such as lead-zirconate-titanate ("PZT"), to produce a high value peripheral capacitor for integration on a common substrate with a ferroelectric memory array also utilizing ferroelectric memory cell capacitors as non-volatile storage elements. The peripheral capacitor is linearly operated in a single direction and may be readily integrated to provide capacitance values on the order of 1-10 nF or more utilizing the same processing steps as are utilized to produce the alternately polarizable memory cell capacitors. The high value peripheral capacitor has application, for example, as a filter capacitor associated with the on-board power supply of a passive radio frequency ("RF") identification ("ID") transponder.

-

Power Supply And Power Enable Circuit For An Rf/Id Transponder

view source -

US Patent:54791723, Dec 26, 1995

-

Filed:Feb 10, 1994

-

Appl. No.:8/194707

-

Inventors:Gregory M. Smith - Colorado Springs CO

Michael W. Yeager - Colorado Springs CO

J. Donald Pauley - Estes Park CO

Gary T. Carroll - Boulder CO -

Assignee:Racom Systems, Inc. - Englewood CO

-

International Classification:G01S 1375

-

US Classification:342 51

-

Abstract:A power supply self-contained within a portable RF/ID transponder includes a full wave rectifier having an input for receiving an antenna signal and outputs for providing power supply and ground voltages, wherein the power supply voltage has a time varying voltage waveform corresponding to the electric field generated by a reader/controller. The power supply further includes a clamping circuit for regulating the power supply voltage and a ferroelectric filter/storage capacitor coupled between the power supply and ground outputs of the full wave rectifier. The power supply further includes a power enable circuit for constantly monitoring the supply voltage waveform and for providing a power enable indication after an initial portion of the supply voltage waveform rises above a predetermined power-up threshold level and for removing the power enable indication when a terminal portion of the supply voltage waveform falls below a predetermined power-down level. The power-up and power-down thresholds describe a proper voltage range of operation for the ferroelectric memory in the transponder. The power enable indication is provided to the ferroelectric memory so that the memory is only operated when the power supply voltage is within the proper range so that data is valid during read and write operations.

Medicine Doctors

Michael W Yeager, Wexford PA

view sourceSpecialties:

Speech-Language Pathology

Address:

5500 Brooktree Rd Suite 102, Wexford, PA 15090

7249403468 (Phone), 7249403969 (Fax)

7249403468 (Phone), 7249403969 (Fax)

Languages:

English

Googleplus

Michael Yeager

Michael Yeager

Michael Yeager

Michael Yeager

Michael Yeager

Michael Yeager

Michael Yeager

Michael Yeager

Plaxo

michael yeager

view sourceowner at hickory hollow landscapers

michael yeager

view sourceHavre de Grace, md

Michael Yeager

view sourceCase Western Reserve University

Youtube

Classmates

Michael Smith (Yeager)

view sourceSchools:

Mt. De Sales Academy Macon GA 1956-1960

Community:

Gerry Schulze, Zackulyn Baybay

Michael Yeager

view sourceSchools:

Perry Meridian High School Indianapolis IN 1986-1990

Michael Yeager

view sourceSchools:

St. Elizabeth High School Pittsburgh PA 1981-1983, South Side Catholic High School Pittsburgh PA 1981-1985

Community:

Lisa Smith, Cynthia Haines, Renee Fanzo, Robert Terleski, Ken Holden, Yvonne Bugielski

Michael Yeager

view sourceSchools:

South Spencer High School Rockport IN 1983-1987

Michael Yeager

view sourceSchools:

Monarch High School Louisville CO 2000-2004

Community:

Caitlin Ripplinger

Michael Yeager

view sourceSchools:

Orland High School Orland CA 1988-1992

Community:

Stephanie Anchors, Darrell Vonasek

Michael Yeager

view sourceSchools:

Corning Elementary School Corning CA 1969-1973

Michael Yeager

view sourceSchools:

Enterprise High School Compton CA 1947-1951

Community:

Bonnie Nash, Terry Thompson, Andy Martin, Elaine Maynard, Lavone Jenkins

Dev Michael Yeager

view source

Michael H Yeager Sr.

view source

Yeager Michael

view source

Nicolette Michael Yeager

view source

Thomas Michael Yeager

view source

Kevin Michael Yeager

view source

Michael Scott Yeager

view source

Michael Henry Yeager

view sourceFlickr

Myspace

Get Report for Michael W Yeager from Colorado Springs, CO, age ~67