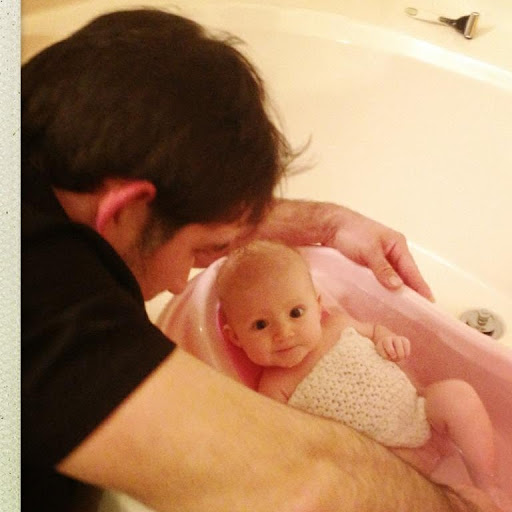

Paul A Mackey

age ~51

from Dripping Springs, TX

- Also known as:

-

- Paul Alan Mackey

- Paula Mackey

Paul Mackey Phones & Addresses

- Dripping Springs, TX

- Black Hawk, CO

- Lakeway, TX

- Universal City, TX

- San Antonio, TX

- 13233 Bright Sky Overlook, Austin, TX 78732

Resumes

Director, Legal Affairs Cabazon Band Of Mission Indians Tribal Government & Fantasy Springs Resort Casino

view sourcePosition:

Legal Affairs Representative at Cabazon Band of Mission Indians

Location:

Palm Springs, California

Industry:

Government Administration

Work:

Cabazon Band of Mission Indians since 2006

Legal Affairs Representative

Legal Affairs Representative

Computer Technician At Energy Star Computers

view sourcePosition:

Computer Technician at Energy Star Computers

Location:

Langhorne, Pennsylvania

Industry:

Information Technology and Services

Work:

Energy Star Computers since Sep 2012

Computer Technician

Word of Life Fellowship Aug 2010 - Jun 2012

Event Coordinator

Applebee's Jan 2007 - Dec 2008

Server

Computer Technician

Word of Life Fellowship Aug 2010 - Jun 2012

Event Coordinator

Applebee's Jan 2007 - Dec 2008

Server

Education:

Liberty University 2010 - 2013

In Progress, Education Word of Life Bible Institute 2008 - 2010

Two Year Non-Degree (Certificate), Bible/Biblical Studies Philadelphia Biblical University 2005 - 2006

Non

In Progress, Education Word of Life Bible Institute 2008 - 2010

Two Year Non-Degree (Certificate), Bible/Biblical Studies Philadelphia Biblical University 2005 - 2006

Non

Paul Mackey

view sourceLocation:

United States

Senior Manager At Advanced Micro Devices

view sourcePosition:

Senior Manager at Advanced Micro Devices

Location:

Austin, Texas Area

Industry:

Semiconductors

Work:

Advanced Micro Devices

Senior Manager

Senior Manager

Education:

The University of Texas at Austin 1997 - 1998

BS, Electrical engineering

BS, Electrical engineering

Paul Mackey

view sourceLocation:

United States

Paul Mackey

view sourceLocation:

United States

Name / Title

Company / Classification

Phones & Addresses

MGM CUSTOM HOMES LC

Us Patents

-

Power Management In A Communication Link

view source -

US Patent:7607031, Oct 20, 2009

-

Filed:Jul 7, 2006

-

Appl. No.:11/482269

-

Inventors:Paul A. Mackey - Austin TX, US

Paul C. Miranda - Austin TX, US

Larry D. Hewitt - Austin TX, US

Jonathan M. Owen - Northborough MA, US -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 1/26

-

US Classification:713300, 713310, 713323

-

Abstract:A computer system includes a first and a second integrated circuit coupled by a communication link. The communication link operates in a power savings mode in which data is not transmitted over the link. Periodically, the communication link enters a training phase in which training patterns are transmitted over the communication link for a predetermined time period. The communication link returns to the power savings mode after the predetermined time period has elapsed. At least one sideband signal, separate from the communication link, and coupled between the first and second integrated circuits, is used to indicate when to enter the training phase from the power savings mode and exit the training phase and return to the power savings mode.

-

In-Band Power Management In A Communication Link

view source -

US Patent:7617404, Nov 10, 2009

-

Filed:Jul 7, 2006

-

Appl. No.:11/482211

-

Inventors:Paul A. Mackey - Austin TX, US

Paul C. Miranda - Austin TX, US

Larry D. Hewitt - Austin TX, US

Jonathan M. Owen - Northborough MA, US -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 1/26

-

US Classification:713300, 713320, 713323

-

Abstract:A first portion of a communication link is operated in a power savings mode at the same time that a second portion of the communication link is operated in a normal operational mode. For the first portion, a refresh mode is entered from the power savings mode in which one or more training patterns are transmitted over the first portion, while the second portion remains in the normal operational mode. An indication when to activate and deactivate the refresh mode may be sent over the second portion of the communication link. The refresh mode may be periodically entered from the power savings mode based on an interval register specifying the amount of time the communication link should remain in the power savings mode before a refresh occurs. In addition, the amount of time spent in the refresh mode may be programmable.

-

Selective Deactivation Of Processor Cores In Multiple Processor Core Systems

view source -

US Patent:7856562, Dec 21, 2010

-

Filed:May 2, 2007

-

Appl. No.:11/743341

-

Inventors:Alexander Branover - Brookline MA, US

Maurice Steinman - Marlborough MA, US

Frank Helms - Austin TX, US

Bill K. C. Kwan - Austin TX, US

W. Kurt Lewchuk - Austin TX, US

Paul Mackey - Austin TX, US -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 1/26

-

US Classification:713300, 713320

-

Abstract:A method includes applying a voltage to a first processor core of a plurality of processor cores to deactivate the first processor core, the voltage less than a retention voltage of the first processor core. The application of the voltage can be in response to a software setting. The software setting can be configured via a user input, a software application, an operating system, or a BIOS setting. Alternately, the application of the voltage can be in response to a permanent hardware setting, such as the state of a fuse associated with the first processor core.

-

Dynamic Processor Power Management Device And Method Thereof

view source -

US Patent:7870407, Jan 11, 2011

-

Filed:May 18, 2007

-

Appl. No.:11/750365

-

Inventors:Alex Branover - Brookline MA, US

Frank P. Helms - Austin TX, US

Jonathan M. Owen - Northboro MA, US

Kurt Lewchuk - Austin TX, US

Maurice Steinman - Marlborough MA, US

Paul Mackey - Austin TX, US -

Assignee:Advanced Micro Devices, Inc. - Sunnyvale CA

-

International Classification:G06F 1/32

-

US Classification:713323, 713300, 713310, 713320, 713330

-

Abstract:A processor can operate in different power modes. In an active power mode, the processor executes software. In response to receiving a halt indication from the software, hardware at the processor evaluates bus transactions for the processor. If the bus transactions meet a heuristic, hardware places a processor core in a lower power mode, such as a retention mode. Because the bus transactions are evaluated by hardware, rather than by software, and the software is not required to perform handshakes and other protocols to place the processor in the lower power mode, the processor is able to place the processor core into the lower power mode more quickly, thereby conserving power.

Lawyers & Attorneys

Paul Mackey - Lawyer

view sourceISLN:

905271888

Admitted:

1974

University:

Rutgers University, B.A., 1969

Law School:

Rutgers University, J.D., 1974

Paul Mackey - Lawyer

view sourceISLN:

905271918

Admitted:

1979

University:

College of the Holy Cross, B.A., 1974

Law School:

George Mason University, J.D., 1979

Paul Mackey - Lawyer

view sourceOffice:

Schiff Hardin LLP

Specialties:

General Practice

Construction & Development

Real Estate

Finance

Construction & Development

Real Estate

Finance

ISLN:

905271895

Admitted:

1988

University:

Manhattan College, B.S., 1985

Law School:

St. John's University School of Law, J.D., 1988

Googleplus

Paul Mackey

Work:

NASA - Engineer

Paul Mackey

Paul Mackey

Paul Mackey

Paul Mackey

Paul Mackey

Paul Mackey

Paul Mackey

Plaxo

Paul Mackey

view sourcePyramid Brokerage Company

Youtube

Classmates

Paul MacKey

view sourceSchools:

Horace Mann Elementary School Chicago IL 1977-1978

Community:

Alfred Sunderland, Angela Green

Paul MacKey

view sourceSchools:

Bangor Lincoln School Bay City MI 1984-1990, Christa McAuliffe Middle School Bay City MI 1990-1992

Community:

Rick Ropp

Paul MacKey

view sourceSchools:

Booth Memorial High School St. John's Peru 1980-1984

Community:

Gloria Stone, Gary Holwell, Joyce Reeves

Paul Mackey

view sourceSchools:

East Syracuse-Minoa Central High School East Syracuse NY 1969-1973

Community:

Sandra Matteson, Raymond Dipietro

Paul MacKey

view sourceSchools:

Horace O'Bryant Middle School Key West FL 1964-1968

Community:

Ellen Singler, Jacquelyn Stevens, Arnaldo Boza

Paul MacKey

view sourceSchools:

Peterborough High School Peterborough Morocco 1965-1969

Community:

Kim Bailey, Rachel Petroff

Paul Mackey

view sourceSchools:

John G. Leach School New Castle DE 1970-1974

Community:

William Ziegler, Francis Gordy, Regina Edwards, Iris Coover, Brian Fleischut, Chelsea Keplinger

Paul MacKey

view sourceSchools:

St. Anne School Hanmer Morocco 1976-1983, St. Anne School Sudbury Morocco 1980-1984, Nickel District Secondary School Sudbury Morocco 1985-1988

Community:

Kenneth Bolton, Thomas Malakasis, Joyce Stevenson, Mariam Mansourian

Paul Mackey

view source

Paul Mackey

view source

Paul Mackey

view source

Paul Mackey

view source

Paul Britton Mackey

view source

Paul Mackey

view source

Paul Gregory Mackey

view source

Paul Mackey

view sourceFlickr

Myspace

Get Report for Paul A Mackey from Dripping Springs, TX, age ~51