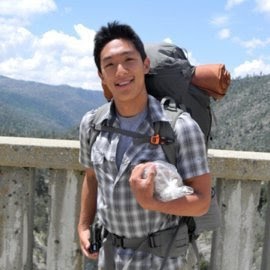

Stephen Boheng Li

age ~34

from New York, NY

- Also known as:

-

- Stephen B Li

- Phone and address:

-

75 W End Ave, New York, NY 10023

6462343763

Stephen Li Phones & Addresses

- 75 W End Ave, New York, NY 10023 • 6462343763

- San Francisco, CA

- Allen, TX

- South San Francisco, CA

- Chicago, IL

- Plano, TX

- 601 Leavenworth St APT 45, San Francisco, CA 94109 • 4158856439

Work

-

Company:Wind river systems, inc.

-

Address:500 Wind River Way, New York, NY 10036

-

Phones:2127733000

-

Position:Vice president offshore engineering

-

Industries:Engineering Services

Lawyers & Attorneys

Name / Title

Company / Classification

Phones & Addresses

Vice President Offshore Engineering

Wind River Systems, Inc.

Engineering Services

Engineering Services

500 Wind River Way, New York, NY 10036

President

The Li Architectural Corporation

Architectural Services

Architectural Services

255 Berry St, San Francisco, CA 94158

Director, Treasurer

PLANO INTERNATIONAL FESTIVAL CORPORATION

Business Services at Non-Commercial Site · Nonclassifiable Establishments

Business Services at Non-Commercial Site · Nonclassifiable Establishments

8332 Barber Oak Dr, Plano, TX 75025

4312 Benton Elm Dr, Plano, TX 75024

3312 Aqua Spg, Plano, TX 75025

4312 Benton Elm Dr, Plano, TX 75024

3312 Aqua Spg, Plano, TX 75025

Data Processing Staff, MIS Director, Vice-President

Liberty Healthcare System Inc

General Hospital

General Hospital

355 Grand St, Jersey City, NJ 07302

2019152000

2019152000

Chief Information Officer, Chief Technology Officer

Jersey City Medical Center

Medical Doctor's Office · General Hospital · Anesthesiology · Thoracic Surgery · Colon Care · Surgeons · Hospitalist · Emergency Medicine

Medical Doctor's Office · General Hospital · Anesthesiology · Thoracic Surgery · Colon Care · Surgeons · Hospitalist · Emergency Medicine

355 Grand St, Jersey City, NJ 07302

395 Grand St, Jersey City, NJ 07302

50 Grand St, Jersey City, NJ 07302

2019152000, 2019152486, 2019152600, 2019152219

395 Grand St, Jersey City, NJ 07302

50 Grand St, Jersey City, NJ 07302

2019152000, 2019152486, 2019152600, 2019152219

CLEW Z. ANGUS (USA) INC

15 Greenwich Ave, New York, NY 10014

15 Greenwich Ve, New York, NY 10014

42 Cricketown Rd, Stony Point, NY 10980

15 Greenwich Ve, New York, NY 10014

42 Cricketown Rd, Stony Point, NY 10980

Managing

Centillion Transnational LLC

5 Col Conklin Dr, Stony Point, NY 10980

1158 1 Ave, New York, NY 10065

1158 1 Ave, New York, NY 10065

Vice-President

LINUX TECH, INC

Computer Software Consulting & Integration Networking and Hardware

Computer Software Consulting & Integration Networking and Hardware

1701 N Greenville Ave STE 1102, Richardson, TX 75081

1751 Jay Ell Dr, Richardson, TX 75081

876 N Glenville Dr, Richardson, TX 75081

9729070871

1751 Jay Ell Dr, Richardson, TX 75081

876 N Glenville Dr, Richardson, TX 75081

9729070871

Us Patents

-

Weighted Round-Robin Arbitrator

view source -

US Patent:7512148, Mar 31, 2009

-

Filed:Dec 9, 2003

-

Appl. No.:10/731810

-

Inventors:Stephen Li - Plano TX, US

Brian Tse Deng - Richardson TX, US -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:H04J 3/02

-

US Classification:370462, 370412, 370415, 370417

-

Abstract:A weighted round-robin arbitrator for a plurality of data queue includes an arbitration table comprising a plurality of entries. Each entry represents a time slot for the transmission of one data packet from a selected one of the plurality of data queues. There is one arbitration logic circuit for each of the plurality of entries in the arbitration table. Each arbitration logic circuit includes a first multiplexer receiving an output from a first table entry and an output from a second table entry in the arbitration table. A second multiplexer receives empty flags from each of the data queues, the flags indicating that there is no data to the sent from that queue. An output of the second multiplexer is coupled to a control input of the first multiplexer so that the first table entry value is output from the first multiplexer if the corresponding queue has data to be sent out and the second table entry value is sent out from the first multiplexer if the queue corresponding to that table entry has data to be sent out and the queue corresponding to the first entry has no data to be sent out.

-

Pci Express Switch

view source -

US Patent:20050125590, Jun 9, 2005

-

Filed:Dec 9, 2003

-

Appl. No.:10/731743

-

Inventors:Stephen Li - Plano TX, US

Brian Deng - Richardson TX, US

Paul Howard - Richardson TX, US

Dave Kimble - Carrollton TX, US -

International Classification:G06F013/00

-

US Classification:710317000

-

Abstract:A PCI Express switch utilizes a central crossbar memory for all ports of the switch. The crossbar memory retains the packet that is to be sent out and only the head pointer for the packet is transmitted to the transmission port. The crossbar memory can also be used as the replay memory for the switch. A circuit for choosing the head pointer at a port for the packet to be sent out, is also disclosed.

-

Method And Apparatus For Data Stream Management

view source -

US Patent:20080222370, Sep 11, 2008

-

Filed:Mar 10, 2008

-

Appl. No.:12/045267

-

Inventors:Fitzgerald J Archibald - Bangalore, IN

Stephen Hsiao-Yi Li - Plano TX, US

Michael O. Polley - Garland TX, US

Mohamed F. Mansour - Richardson TX, US

Ramesh Naidu G - Anantapur, IN -

Assignee:TEXAS INSTRUMENTS INCORPORATED - Dallas TX

-

International Classification:G06F 12/00

-

US Classification:711154, 711E12001

-

Abstract:A method and apparatus of managing data stream, the method comprising archiving received data in a circular buffer; utilizing a breakpoint in realizing the archived received data continuity, wherein the breakpoint is set to the last data portion of the archived received data; when the archiving of the received data approaches the end of the circular buffer, stitching the last portion of the archived received data to the start of the circular buffer; and setting the breakpoint to the updated last data portion of the archived data.

-

Optimizing Task Management

view source -

US Patent:20110271076, Nov 3, 2011

-

Filed:Apr 28, 2010

-

Appl. No.:12/769080

-

Inventors:Maarten Koning - Bloomfield, CA

Stephen Li - Menlo Park CA, US -

International Classification:G06F 15/80

G06F 9/46 -

US Classification:712 20, 718100

-

Abstract:An electronic device includes a processing component and a task manager. The processing component is configurable for one of a single-core processing mode and a multi-core processing mode. The task manager determines a number of tasks running on the electronic device. The processor is configured to one of the single-core processing mode and the multi-core processing mode as a function of the number of tasks.

-

System Decoder Circuit And Method Of Operation

view source -

US Patent:56318480, May 20, 1997

-

Filed:Jun 7, 1995

-

Appl. No.:8/486487

-

Inventors:Frank L. Laczko - Allen TX

Gerard Benbassat - St. Paul de Vence, FR

Stephen H. Li - Garland TX -

Assignee:Texas Instruments - Dallas TX

-

International Classification:G06F 1900

-

US Classification:364514R

-

Abstract:A data processing system (10) is disclosed which comprises a microprocessor host (12) coupled to a decoding system (14). A host interface block (18) receives a bit stream and passes bit stream on to a system decoder block (20). The system decoder block (20) extracts the appropriate data from the bit stream and loads an input buffer (24) or an optional external buffer (26). An audio decoder block (28) retrieves the data from the input buffer (24) and generates scale factor indices, bit per code word values and subband samples which are stored in an arithmetic unit buffer (30). A hardware filter arithmetic unit block (32) retrieves the information from the arithmetic unit buffer (30) and dequantizes, transforms and filters the data to generate PCM output data which is loaded into a PCM buffer (34). The data within the PCM buffer (34) is output by a PCM output block (36) to a digital-to-analog converter (16).

-

System Decoder Circuit With Temporary Bit Storage And Method Of Operation

view source -

US Patent:56424370, Jun 24, 1997

-

Filed:Apr 26, 1993

-

Appl. No.:8/054126

-

Inventors:Frank L. Laczko - Allen TX

Gerard Benbassat - St. Paul de Vence, FR

Stephen H. Li - Garland TX -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:H03M 740

-

US Classification:382246

-

Abstract:A data processing system (10) is disclosed which comprises a microprocessor host (12) coupled to a decoding system (14). A host interface block (18) receives a bit stream and passes bit stream on to a system decoder block (20). The system decoder block (20) extracts the appropriate data from the bit stream and loads an input buffer (24) or an optional external buffer (26). An audio decoder block (28) retrieves the data from the input buffer (24) and generates scale factor indices, bit per code word values and subband samples which are stored in an arithmetic unit buffer (30). A hardware filter arithmetic unit block (32) retrieves the information from the arithmetic unit buffer (30) and dequantizes, transforms and filters the data to generate PCM output data which is loaded into a PCM buffer (34). The data within the PCM buffer (34) is output by a PCM output block (36) to a digital-to-analog converter (16).

-

Method For Processing A Subband Encoded Audio Data Stream

view source -

US Patent:57941815, Aug 11, 1998

-

Filed:Mar 24, 1997

-

Appl. No.:8/824072

-

Inventors:Gerard Benbassat - St. Paul de Vence, FR

Frank L. Laczko - Allen TX

Stephen H. Li - Garland TX

Kenneth R. Cyr - Carrollton TX

Jonathan L. Rowlands - Dallas TX -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:G10L 302

G10L 900 -

US Classification:704212

-

Abstract:A data processing system (10) is disclosed which comprises a microprocessor host (12) coupled to a decoding system (14). A host interface block (18) receives a bit stream and passes bit stream on to a system decoder block (20). The system decoder block (20) extracts the appropriate data from the bit stream and loads an input buffer (24) or an optional external buffer (26). An audio decoder block (28) retrieves the data from the input buffer (24) and generates scale factor indices, bit per code word values and subband samples which are stored in an arithmetic unit buffer (30). A hardware filter arithmetic unit block (32) retrieves the information from the arithmetic unit buffer (30) and dequantizes, transforms and filters the data to generate PCM output data which is loaded into a PCM buffer (34). The data within the PCM buffer (34) is output by a PCM output block (36) to a digital-to-analog converter (16).

-

Digital Crossbar Switch

view source -

US Patent:48520837, Jul 25, 1989

-

Filed:Jun 22, 1987

-

Appl. No.:7/065231

-

Inventors:Jeffrey A. Niehaus - Dallas TX

Robert G. Fleck - Dallas TX

Stephen Li - Garland TX

Bob D. Strong - Garland TX -

Assignee:Texas Instruments Incorporated - Dallas TX

-

International Classification:H04M 318

-

US Classification:370 58

-

Abstract:A digital crossbar switch for switching data from an input/output data bus to an internal data bus and to the same or another input/output data bus which includes a plurality of multiplexer logic units, an m-bit internal data bus coupled to each of said multiplexer logic units where m is an integer, and a plurality of n-bit input/output data buses one connected to each of the multiplexer logic units were n is an integer. The switch further includes an m/n to 1 multiplexer, where m/n is an integer, in each multiplexer logic unit. The m/n to 1 multiplexer has an input control to the internal data bus and an output coupled to a corresponding one of the input/output data buses and is operative in response to a configuration control signal to switch a selected n-bits of data from the internal data bus to the corresponding input/output data bus. A memory storage for storing configuration control signals is coupled to the m/n to 1 multiplexer.

Stephen Li ()

view source

Stephen Li Bi

view source

Stephen Z. Li

view source

Stephen Li

view source

Peng Fei Stephen Li ()

view source

Stephen Li

view source

Stephen Li

view source

HanXuan Stephen Li

view sourceYoutube

Plaxo

STEPHEN K. LI

view source4 Lansing Square, Unit 203, N.Y., ON. M2J5A2Mortgage Broker at Centum One Financial Group A Real Estate Broker and Mortgage Broker, who is a trained professional and knows how to effectively handle Buyers and Sellers alike. As a full-time... A Real Estate Broker and Mortgage Broker, who is a trained professional and knows how to effectively handle Buyers and Sellers alike. As a full-time Residential, Commercial Broker and Mortgage Broker, I welcome the opportunity to put my personal expertise and company resources to work for you.

Stephen Li

view source

STEPHEN LI

view sourceTreasury Officer at HSH Management Services Ltd

Googleplus

Stephen Li

Work:

Beijing Chang Wen Si Qi Network Technology Co. - Co-founder/Technical Director (2011-2013)

Microsoft - Technical Program Manager (2009-2010)

Microsoft - Software Development Engineer (2007-2009)

Microsoft - Technical Program Manager (2009-2010)

Microsoft - Software Development Engineer (2007-2009)

Education:

Shanghai Jiao Tong University - Software Engineering

Tagline:

Tech pm, ios dev

Stephen Li

Work:

TAIPING TRADING - PURCHASING OFFICER

TAIPING NEWLYNN - TAIPING NEWLYNN ASSISTANT MANAGER

TAIPING NEWLYNN - TAIPING NEWLYNN ASSISTANT MANAGER

Education:

AUT - BUSINESS

About:

TAIPING TRADING CO LTD PURCHASING OFFICER

Tagline:

NO NEED RUSH, BUY QUICK!

Stephen Li

Lived:

San Francisco, CA

Work:

Lumos Labs - Software Engineer

Education:

University of California, Berkeley - EECS

Tagline:

Bloop

Stephen Li

Work:

Amphenol - Engineering Assistant (2011-2011)

Rich Media - Programmer Analyst (2011-2011)

Rich Media - Programmer Analyst (2011-2011)

Education:

University of Waterloo - Mechatronics Engineering

Stephen Li

Work:

O2 skypark

Education:

Wallace high school

Stephen Li

Education:

University of Notre Dame - MBA

Tagline:

Onebowl

Stephen Li

Education:

University of California, Santa Cruz, South Pasadena High School

Stephen Li

Education:

Florida Institute of Technology - Mechanical Engineering

Get Report for Stephen Boheng Li from New York, NY, age ~34