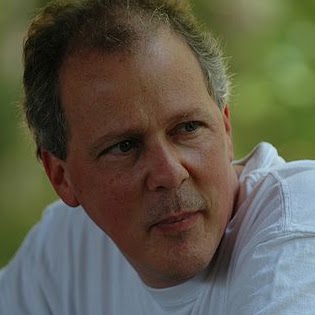

Walker E Anderson

age ~61

from San Marcos, CA

- Also known as:

-

- Walker Su Anderson

- Walker E Andersen

- Walter Anderson

- Edward Andersonwalker

- Edward Anderson Walker

Walker Anderson Phones & Addresses

- San Marcos, CA

- 12438 Creekview Dr, San Diego, CA 92128 • 8585134146

- 986 Gardenia Ct, San Marcos, CA 92078

Work

-

Position:Machine Operators, Assemblers, and Inspectors Occupations

Education

-

Degree:High school graduate or higher

Resumes

Marcom Chair At Atlanta Film Festival

view sourcePosition:

MarCom Chair at Atlanta Film Festival, Sales, Marketing & Product Mgmt at Comcast

Location:

Atlanta, Georgia

Industry:

Marketing and Advertising

Work:

Atlanta Film Festival - Greater Atlanta Area since Jul 2012

MarCom Chair

Comcast - Greater Atlanta Area since Oct 2006

Sales, Marketing & Product Mgmt

Atlanta Film Festival - Greater Atlanta Area Jun 2010 - Jun 2012

Chairman/President

Atlanta Film Festival Jul 2008 - Jun 2010

Board Member

Comcast - Greater Atlanta Area Oct 2006 - Feb 2010

Partnership Marketing & Media Management

MarCom Chair

Comcast - Greater Atlanta Area since Oct 2006

Sales, Marketing & Product Mgmt

Atlanta Film Festival - Greater Atlanta Area Jun 2010 - Jun 2012

Chairman/President

Atlanta Film Festival Jul 2008 - Jun 2010

Board Member

Comcast - Greater Atlanta Area Oct 2006 - Feb 2010

Partnership Marketing & Media Management

Education:

University of Virginia 2002 - 2006

Bachelor of Arts Westminster 2002

Bachelor of Arts Westminster 2002

Skills:

Marketing Strategy

Product Life Cycle Management

Conflict Resolution

Media Planning

Adobe Creative Suite

Forecasting

Graphic Design

Product Management

Contract Negotiation

Non-profit Administration

Strategic Partnerships

Sponsorship

Digital Media

New Media

Television

Product Life Cycle Management

Conflict Resolution

Media Planning

Adobe Creative Suite

Forecasting

Graphic Design

Product Management

Contract Negotiation

Non-profit Administration

Strategic Partnerships

Sponsorship

Digital Media

New Media

Television

Interests:

marketing, music, new technology, film, sports, gaming

Honor & Awards:

Athletic Hall of Fame, Westminster Schools; 2011

Comcast Sports Monthly Best Practice: Bleachers On Demand (11/09)

Atlanta Track Club Man of the Year: (Field, 2001, 2002)

Atlantic Coast Conference Honor Role (UVA)

Staff Engineer

view sourceLocation:

San Diego, CA

Industry:

Semiconductors

Work:

Luxtera, Inc.

Staff Engineer

Staff Engineer

Walker Anderson

view sourceLocation:

San Diego, CA

Industry:

Semiconductors

Work:

Arm Apr 2006 - Oct 2008

Field Applications Engineer

Applied Micro Circuits Corporation 1995 - 2004

Design Engineer

Field Applications Engineer

Applied Micro Circuits Corporation 1995 - 2004

Design Engineer

Education:

Uc San Diego 1991 - 1995

Skills:

Semiconductors

Walker Anderson

view source

Walker Anderson

view sourceLocation:

San Diego, CA

Us Patents

-

Elastic Store Circuit With Vernier Clock Delay

view source -

US Patent:6629251, Sep 30, 2003

-

Filed:Oct 20, 1999

-

Appl. No.:09/420983

-

Inventors:Walker Edward Anderson - San Diego CA

Thomas Gordon Palkert - Excelsior MN

Robert S. Tepper - San Diego CA -

Assignee:Applied Micro Circuits Corporation - San Diego CA

-

International Classification:G06F 112

-

US Classification:713401, 713400, 713600, 710 52

-

Abstract:An elastic store circuit using a first in/first out buffer (FIFO) to accurately delay and manipulate a waveform using the write (WR) and read (RD) clocks is provided. The FIFO delays data by, first, reading the input data at the WR clock rate. Then, the data exits the FIFO in response to the RD clock. Large delays are accomplished by changing the relationship between the WR and RD clocks in whole clock intervals. Delays and adjustments of less than a whole clock interval are accomplished by changing the phase relationship of the RD clock with respect to the WR clock. The present invention generates the WR and RD clocks through synthesis using a lower frequency reference clock. The RD phase change results from introducing a phase change into the reference clock driving the RD clock synthesizer. A method of introducing precise delays through phase control of the WR and RD clocks is also provided.

-

Elastic Store Circuit With Static Phase Offset

view source -

US Patent:6681272, Jan 20, 2004

-

Filed:Oct 20, 1999

-

Appl. No.:09/420976

-

Inventors:Walker Edward Anderson - San Diego CA

Thomas Gordon Palkert - Excelsior MN

Robert S. Tepper - San Diego CA -

Assignee:Applied Micro Circuits Corporation - San Diego CA

-

International Classification:G06F 1314

-

US Classification:710 52, 713400, 713401, 375375, 375372

-

Abstract:An elastic store circuit using a first in/first out buffer (FIFO) to accurately control the phase delay in a waveform using the write (WR) and read (RD) clocks is provided. The FIFO reads the input data at the WR clock rate. The data exits the FIFO in response to the RD clock. Large delays are accomplished by changing the relationship between the WR and RD clocks in whole clock intervals. Delays and adjustments of less than a whole clock interval are accomplished by changing the phase relationship of the RD clock with respect to the WR clock. The present invention generates the WR and RD clocks through synthesis using a lower frequency reference clock. The RD clock phase change results from phase-locking the RD clock to a phase offset version of the reference clock. A method of introducing precise delays through phase delay of the RD clock with respect to the reference clock is also provided.

Walker Anderson

view source

Walker Anderson

view source

Walker Anderson

view source

Walker Anderson

view source

Walker Anderson

view source

Walker C. Anderson

view source

Walker Anderson

view source

Walker Anderson

view sourceYoutube

Myspace

Classmates

Ethel Marie Walker (Ander...

view sourceGoogleplus

Walker Anderson

Education:

Randolph Community College - Photography

About:

I am a photography student at RCC. Im 19 years old from Clayton, NC.

Tagline:

I am a 19 year old photographer

Walker Anderson

Education:

The Creative Center - Graphic Design

Walker Anderson

Walker Anderson

Walker Anderson

Walker Anderson

Walker Anderson

Walker Anderson

Get Report for Walker E Anderson from San Marcos, CA, age ~61