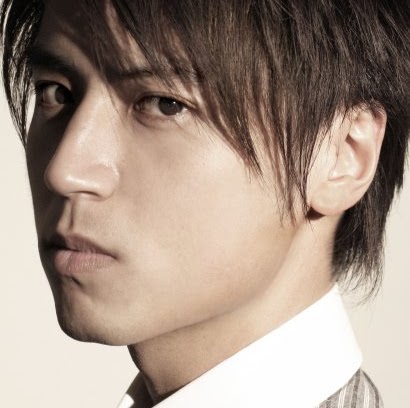

Yang Li

age ~36

from Houston, TX

- Also known as:

-

- Li Yang

Yang Li Phones & Addresses

- Houston, TX

- Minneapolis, MN

- Saint Paul, MN

Name / Title

Company / Classification

Phones & Addresses

Director

FOCUS HEADWEAR, INC

2913 Anode Ln, Dallas, TX 75220

9846 Harwin Dr, Houston, TX 77036

2951 Ladybird Ln, Dallas, TX 75220

1701 N Greenville Ave, Richardson, TX 75081

9846 Harwin Dr, Houston, TX 77036

2951 Ladybird Ln, Dallas, TX 75220

1701 N Greenville Ave, Richardson, TX 75081

Director

KENVIC CORPORATION

1502 Whispering Pne Dr, Houston, TX 77055

Director

LIQIU INC

6100 Corporate Dr STE 588, Houston, TX 77036

9201 Clarewood #345, Houston, TX 77036

9201 Clarewood #345, Houston, TX 77036

Director, President

CELLPHONE DEPOT, INC

Ret Misc Merchandise

Ret Misc Merchandise

9888 Bellaire Blvd STE 112, Houston, TX 77036

PO Box 740289, Houston, TX 77274

907 Alexandra St, Stafford, TX 77477

PO Box 740289, Houston, TX 77274

907 Alexandra St, Stafford, TX 77477

Director

L&L ART BUILDER CO

7445 Wanda Ln, Houston, TX 77074

Director, Managing

NOVA HAY & GRAIN, LLC

Whol Grain/Field Beans

Whol Grain/Field Beans

5855 Sovereign Dr STE A, Houston, TX 77036

PO Box 740289, Houston, TX 77274

907 Alexandria St, Stafford, TX 77477

907 Alexandra St, Stafford, TX 77477

PO Box 740289, Houston, TX 77274

907 Alexandria St, Stafford, TX 77477

907 Alexandra St, Stafford, TX 77477

Director, Managing

TOP HAY, LLC

Whol Grain/Field Beans

Whol Grain/Field Beans

9999 Bellaire Blvd STE 8B, Houston, TX 77036

6100 Corporate Dr, Houston, TX 77036

6100 Corporate Dr, Houston, TX 77036

Managing M, Director, Managing

LAIRD MANUFACTURING CHINA, LLC

9999 Bellaire Blvd STE 8B, Houston, TX 77036

5855 Sovereign Dr, Houston, TX 77036

PO Box 740289, Houston, TX 77036

5855 Sovereign Dr, Houston, TX 77036

PO Box 740289, Houston, TX 77036

Medicine Doctors

Yang Li

view sourceLicense Records

Yang Li

License #:

009176

Category:

Respiratory Therapist

Issued Date:

May 12, 2015

Type:

RESPIRATORY THERAPY

Lawyers & Attorneys

Us Patents

-

Ferroelectric Memory Using Multiferroics

view source -

US Patent:7700985, Apr 20, 2010

-

Filed:Jun 24, 2008

-

Appl. No.:12/144697

-

Inventors:Haiwen Xi - Prior Lake MN, US

Wei Tian - Bloomington MN, US

Yang Li - Shoreview MN, US

Insik Jin - Eagan MN, US

Song S. Xue - Edina MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:H01L 29/94

G11C 16/06 -

US Classification:257297, 36518522

-

Abstract:Ferroelectric memory using multiferroics is described. The multiferroic memory includes a substrate having a source region, a drain region and a channel region separating the source region and the drain region. An electrically insulating layer is adjacent to the source region, drain region and channel region. A data storage cell having a composite multiferroic layer is adjacent to the electrically insulating layer. The electrically insulating layer separated the data storage cell form the channel region. A control gate electrode is adjacent to the data storage cell. The data storage cell separates at least a portion of the control gate electrode from the electrically insulating layer.

-

Non-Volatile Memory Cell With Enhanced Filament Formation Characteristics

view source -

US Patent:7795606, Sep 14, 2010

-

Filed:Oct 30, 2008

-

Appl. No.:12/261137

-

Inventors:Insik Jin - Eagan MN, US

Yang Li - Shoreview MN, US

Dadi Setiadi - Edina MN, US

Song S. Xue - Edina MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:H01L 29/04

-

US Classification:257 3, 257E45002, 438382

-

Abstract:Method and apparatus for constructing a non-volatile memory cell, such as a modified RRAM cell. In some embodiments, a memory cell comprises a resistive storage layer disposed between a first electrode layer and a second electrode layer. Further in some embodiments, the storage layer has a localized region of decreased thickness to facilitate formation of a conductive filament through the storage layer from the first electrode to the second electrode.

-

Nonvolatile Programmable Logic Gates And Adders

view source -

US Patent:7852663, Dec 14, 2010

-

Filed:May 23, 2008

-

Appl. No.:12/125975

-

Inventors:Haiwen Xi - Prior Lake MN, US

Yang Li - Shoreview MN, US

Song S. Xue - Edina MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:G11C 11/00

-

US Classification:365158, 365171, 365173, 365209, 365 66

-

Abstract:Spin torque magnetic logic device having at least one input element and an output element. Current is applied through the input element(s), and the resulting resistance or voltage across the output element is measured. The input element(s) include a free layer and the output element includes a free layer that is electrically connected to the free layer of the input element. The free layers of the input element and the output element may be electrically connected via magnetostatic coupling, or may be physically coupled. In some embodiments, the output element may have more than one free layer.

-

Magnet-Assisted Transistor Devices

view source -

US Patent:7948045, May 24, 2011

-

Filed:Aug 18, 2008

-

Appl. No.:12/193065

-

Inventors:Yang Li - Bloomington MN, US

Insik Jin - Eagan MN, US

Harry Liu - Maple Grove MN, US

Song S. Xue - Edina MN, US

Shuiyuan Huang - Apple Valley MN, US

Michael X. Tang - Bloomington MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:H01L 29/82

H01L 21/00

H01L 21/336 -

US Classification:257421, 257295, 257315, 257427, 257E29272, 257E293, 257E29324, 257E29436, 257E21665, 438 3, 438 48, 438257

-

Abstract:A transistor device includes a magnetic field source adapted to deflect a flow of free electron carriers within a channel of the device, between a source region and a drain region thereof. According to preferred configurations, the magnetic field source includes a magnetic material layer extending over a side of the channel that is opposite a gate electrode of the transistor device.

-

Magnetic Floating Gate Memory

view source -

US Patent:7961503, Jun 14, 2011

-

Filed:Jan 19, 2009

-

Appl. No.:12/355908

-

Inventors:Insik Jin - Eagan MN, US

Yang Li - Shoreview MN, US

Hongyue Liu - Maple Grove MN, US

Song S. Xue - Edina MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:G11C 11/00

-

US Classification:365158, 36518518

-

Abstract:An apparatus includes at least one memory device including a floating gate element and a magnetic field generator that operably applies a magnetic field to the memory device. The magnetic field directs electrons in the memory device into the floating gate element.

-

Transmission Gate-Based Spin-Transfer Torque Memory Unit

view source -

US Patent:7974119, Jul 5, 2011

-

Filed:Jul 10, 2008

-

Appl. No.:12/170549

-

Inventors:Yiran Chen - Eden Prairie MN, US

Hai Li - Eden Prairie MN, US

Hongyue Liu - Maple Grove MN, US

Yong Lu - Rosemount MN, US

Yang Li - Bloomington MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:G11C 11/00

-

US Classification:365158, 365148, 365171, 977935

-

Abstract:A transmission gate-based spin-transfer torque memory unit is described. The memory unit includes a magnetic tunnel junction data cell electrically coupled to a bit line and a source line. A NMOS transistor is in parallel electrical connection with a PMOS transistor and they are electrically connected with the source line and the magnetic tunnel junction data cell. The magnetic tunnel junction data cell is configured to switch between a high resistance state and a low resistance state by passing a polarized write current through the magnetic tunnel junction data cell. The PMOS transistor and the NMOS transistor are separately addressable so that a first write current in a first direction flows through the PMOS transistor and a second write current in a second direction flows through the NMOS transistor.

-

Non-Volatile Programmable Logic Gates And Adders

view source -

US Patent:8179716, May 15, 2012

-

Filed:Nov 24, 2010

-

Appl. No.:12/953544

-

Inventors:Haiwen Xi - Prior Lake MN, US

Yang Li - Shoreview MN, US

Song S. Xue - Edina MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:G11C 11/00

-

US Classification:365158, 365171, 365173, 365209, 365 66

-

Abstract:Spin torque magnetic logic device having at least one input element and an output element. Current is applied through the input element(s), and the resulting resistance or voltage across the output element is measured. The input element(s) include a free layer and the output element includes a free layer that is electrically connected to the free layer of the input element. The free layers of the input element and the output element may be electrically connected via magnetostatic coupling, or may be physically coupled. In some embodiments, the output element may have more than one free layer.

-

Microfabricated Fluid Dynamic Bearing

view source -

US Patent:8192087, Jun 5, 2012

-

Filed:May 27, 2009

-

Appl. No.:12/473243

-

Inventors:Alan L. Grantz - Aptos CA, US

Dadi Setiadi - Edina MN, US

Yang Li - Bloomington MN, US -

Assignee:Seagate Technology LLC - Scotts Valley CA

-

International Classification:F16C 32/06

-

US Classification:384107, 384112, 384110

-

Abstract:A fluid dynamic bearing formed by a microelectromechanical systems (MEMS) wafer-level batch-fabrication process is provided. The process results in a high performance and high reliability fluid dynamic bearing having features including higher bearing lifetime at high RPM, improved bearing stiffness, durability and thrust/restoring forces capabilities. The present invention is especially useful with small form factor disc drive memory devices having constraints in motor height, such as a 2. 5 inch disc drive, requiring high performance including high rotational speed and large areal density. A sacrificial layer is utilized in the process to simultaneously form symmetrical facing surfaces of relatively rotatable components. The facing surfaces define, therebetween, a desired feature, such as a journal bearing, a thrust bearing, a fluid channel, a fluid reservoir, a capillary seal, pressure generating grooves, and other profile geometries. Such geometry control allows for design freedom in obtaining a desired bearing performance and stiffness.

Isbn (Books And Publications)

Science and Technology in China: Selections from the Bulletin of the Chinese Academy of Sciences

view sourceAuthor

Yang Li

ISBN #

0080363865

Zhongguo Nong Cun Ren Shen Bao Xian Shi Chang Yan Jiu: Research on Chinese Rural Life Insurance Market

view sourceAuthor

Yang Li

ISBN #

7802074150

Youtube

Plaxo

Yang Li

view sourceBeijing

Li Yang

view sourceStar Alliance Capital

Li Yang

view source17800 Castleton Street, Suite 165, city of indust...

Flickr

Classmates

Yang LI, Churchill High S...

view source

Yang LI, Jinan University...

view source

Yang LI, Chuanhua High Sc...

view sourceGoogleplus

Yang Li

Work:

Oliver Wyman - Summer Consultant (2011-2011)

Duke Law School - Research Intern (2009-2009)

Duke Law School - Research Intern (2009-2009)

Education:

Yale University - History, Ward Melville High School

Yang Li

Work:

Bourns Inc. - Sales Marketing Coordinator (2007)

Education:

University of California, Riverside - Computer Science, University of California, Riverside - Business Administration

Yang Li

Work:

SpaceX - System Integration Engineer (2008)

Education:

University of Michigan - Aerospace Engineering, Churchill High School - Diploma

Yang Li

Work:

JKL Corporation - Assistant Property Manager (3-6)

Education:

University of California, Merced - Management, University of California, Merced - Psychology

Yang Li

Relationship:

Single

About:

最难解决的是自己吧!

Bragging Rights:

大学毕业了呢~~~

Yang Li

Work:

IBM - Project Manager (2009-2011)

Education:

Beijing University of Aeronautics and Astronautics - Telecommunication

Yang Li

Education:

University of Manchester - Structural Engineering, Hohai University - Mechanical Engineering

Tagline:

Believe me Believe you

Yang Li

Work:

Westin providence - Front desk

Education:

Johnson & Wales University

Tagline:

^^*

Yang Mei Li

view source

Yang Yan Li

view source

Yang Nyit Li

view source

Yang Chin Li

view source

Yang Mey Li

view source

Yang Chee Li

view source

Yang Rui Li

view source

Yang Fui Li

view sourceGet Report for Yang Li from Houston, TX, age ~36